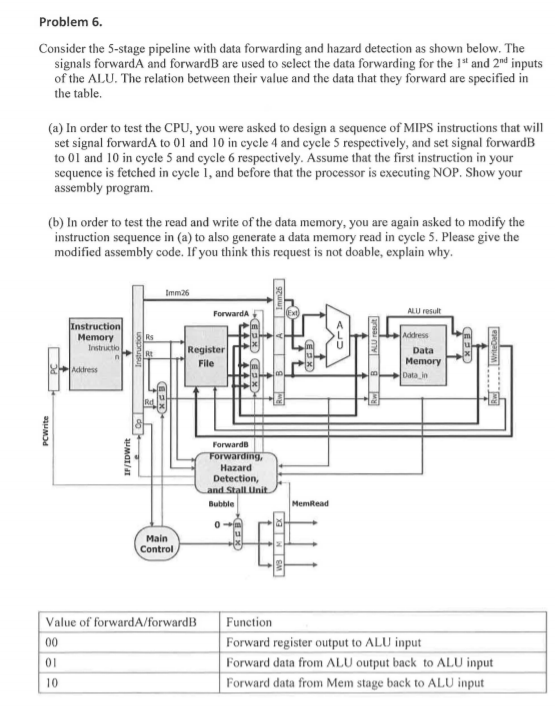

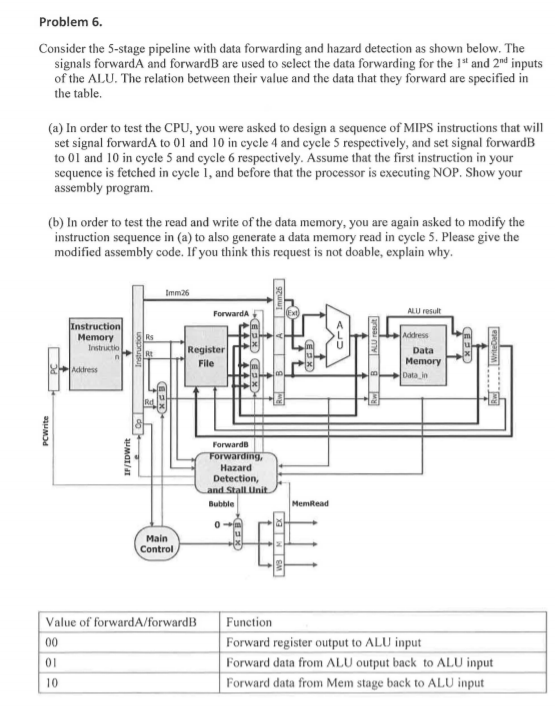

Problem 6. Consider the 5-stage pipeline with data forwarding and hazard detection as shown below. The signals forwardA and forwardB are used to select the data forwarding for the 1st and 2nd inputs of the ALU. The relation between their value and the data that they forward are specified in the table. (a) In order to test the CPU, you were asked to design a sequence of MIPS instructions that will set signal forwardA to 01 and 10 in cycle 4 and cycle 5 respectively, and set signal forwardB to 01 and 10 in cycle 5 and cycle 6 respectively. Assume that the first instruction in your sequence is fetched in cycle 1, and before that the processor is executing NOP. Show your assembly program (b) In order to test the read and write of the data memory, you are again asked to modify the instruction sequence in (a) to also generate a data memory read in cycle 5. Please give the modified assembly code. If you think this request is not doable, explain why. Imm26 Forward ALU result - Instruction Memory Instructio RS Instruction ALU result Register File CXED Address Data Memory Data in WriteData Address Rd 8 PCWrite IF/IDWrit Forward Forwarding, Hazard Detection, and Stall Unit Bubble MemRead 0 Main Control NEM Value of forward A/forwardB 00 01 Function Forward register output to ALU input Forward data from ALU output back to ALU input Forward data from Mem stage back to ALU input 10 Problem 6. Consider the 5-stage pipeline with data forwarding and hazard detection as shown below. The signals forwardA and forwardB are used to select the data forwarding for the 1st and 2nd inputs of the ALU. The relation between their value and the data that they forward are specified in the table. (a) In order to test the CPU, you were asked to design a sequence of MIPS instructions that will set signal forwardA to 01 and 10 in cycle 4 and cycle 5 respectively, and set signal forwardB to 01 and 10 in cycle 5 and cycle 6 respectively. Assume that the first instruction in your sequence is fetched in cycle 1, and before that the processor is executing NOP. Show your assembly program (b) In order to test the read and write of the data memory, you are again asked to modify the instruction sequence in (a) to also generate a data memory read in cycle 5. Please give the modified assembly code. If you think this request is not doable, explain why. Imm26 Forward ALU result - Instruction Memory Instructio RS Instruction ALU result Register File CXED Address Data Memory Data in WriteData Address Rd 8 PCWrite IF/IDWrit Forward Forwarding, Hazard Detection, and Stall Unit Bubble MemRead 0 Main Control NEM Value of forward A/forwardB 00 01 Function Forward register output to ALU input Forward data from ALU output back to ALU input Forward data from Mem stage back to ALU input 10