Answered step by step

Verified Expert Solution

Question

1 Approved Answer

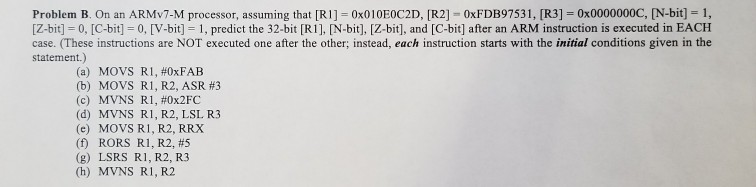

Problem B On an ARMv7-M processor, assuming that [R1] = 0x010E0C2D, [R2]0xFDB97531, R3] = 0x0000000C, N bit1-1, (Z-bit] 0, [C-bit] = 0, [V-bit] = 1,

Problem B On an ARMv7-M processor, assuming that [R1] = 0x010E0C2D, [R2]0xFDB97531, R3] = 0x0000000C, N bit1-1, (Z-bit] 0, [C-bit] = 0, [V-bit] = 1, predict the 32-bit [RI], [N-bit], [Z-bit], and [C-bit] after an ARM instruction is executed in EACH case. (These instructions are NOT executed one after the other; instead, each instruction starts with the initial conditions given in the statement.) (a) MOVS RI, #0xFAB (b) MOVS R1, R2, ASR #3 (c) MVNS RI, #0x2FC (d) MVNS R1, R2, LSL R3 (e) MOVS R1, R2, RRX (f) RORS RI, R2, #5 (g) LSRS RI, R2, R3 (h) MVNS R1, R2

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started