Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Project description: In this project, we need to upgrade our accumulator computer described and implemented in the example above to a bit more complicated computer.

Project description:

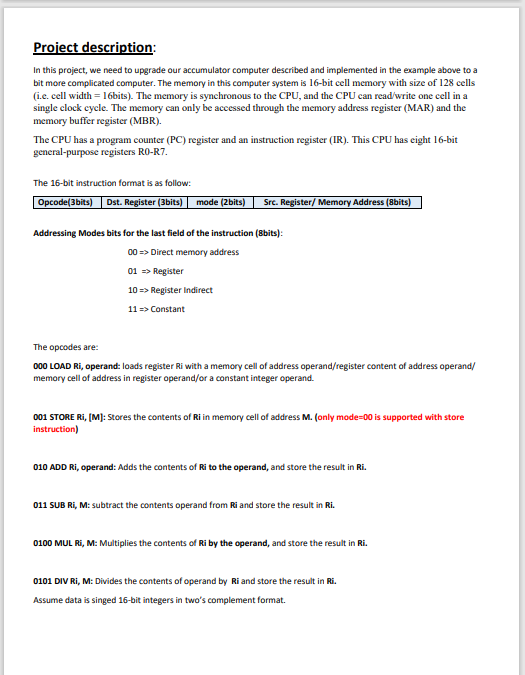

In this project, we need to upgrade our accumulator computer described and implemented in the example above to a

bit more complicated computer. The memory in this computer system is bit cell memory with size of cells

ie cell width bits The memory is synchronous to the CPU, and the CPU can readwrite one cell in a

single clock cycle. The memory can only be aceessed through the memory address register MAR and the

memory buffer register MBR

The CPU has a program counter PC register and an instruction register IR This CPU has eight bit

generalpurpose registers

The bit instruction format is as follow:

Addressing Modes bits for the last field of the instruction bits:

Direct memory address

Register

Register Indirect

Constant

The opcodes are:

O LOAD Ri operand: loads register Ri with a memory cell of address operandregister content of address operand

memory cell of address in register operandor a constant integer operand.

STORE RiM: Stores the contents of Ri in memory cell of address Monly mode is supported with store

instruction

ADD Ri operand: Adds the contents of Ri to the operand, and store the result in Ri

SUB Ri M: subtract the contents operand from Ri and store the result in Ri

MUL Ri M: Multiplies the contents of Ri by the operand, and store the result in Ri

DIV Ri M: Divides the contents of operand by Ri and store the result in Ri

Assume data is singed bit integers in two's complement format. please write full verilog code

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started