Question

Q. Compare and contrast Ripple-Carry Adder and Carry-Look ahead Adder 1) In a 4-bit ripple-carry adder as shown in Figure 5.2, assume that each full-adder

Q. Compare and contrast Ripple-Carry Adder and Carry-Look ahead Adder

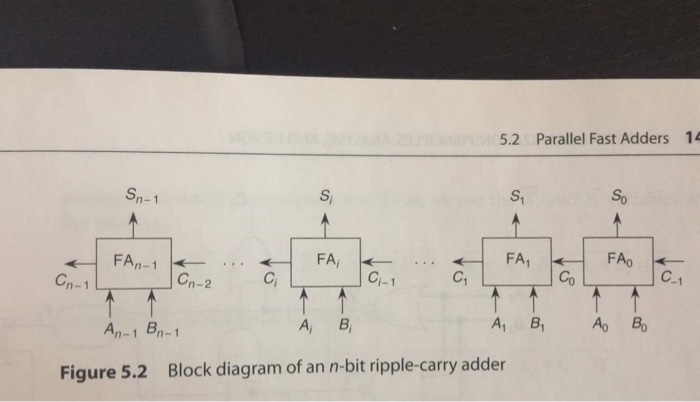

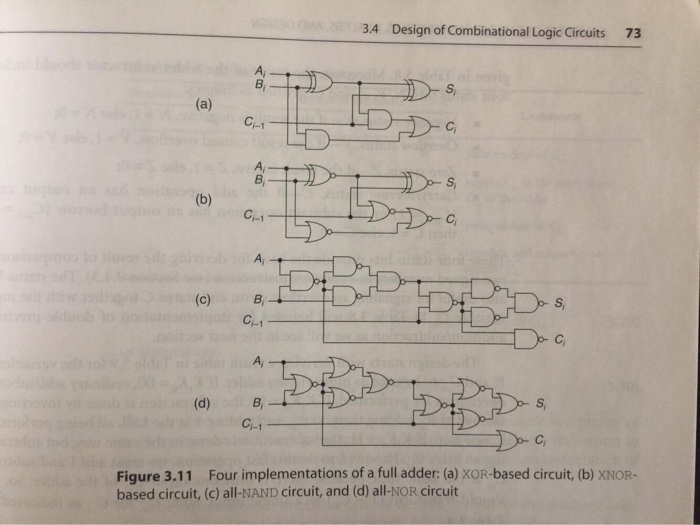

1) In a 4-bit ripple-carry adder as shown in Figure 5.2, assume that each full-adder is implemented using the design as shown in Figure 3.11 (a) and each single logic gate (e.g., AND, OR, XOR, etc.) has a propagation delay of 10 ns. What is the earliest time this 4-bit ripple-carry adder can be sure of having a valid summation output? Explain how you reached your answer and how you did your calculations.

2) In a 16-bit ripple-carry adder as shown in Figure 5.2, what is the earliest time this 16-bit ripple-carry adder can be sure of having a valid summation output? Explain how you reached your answer and how you did your calculations.

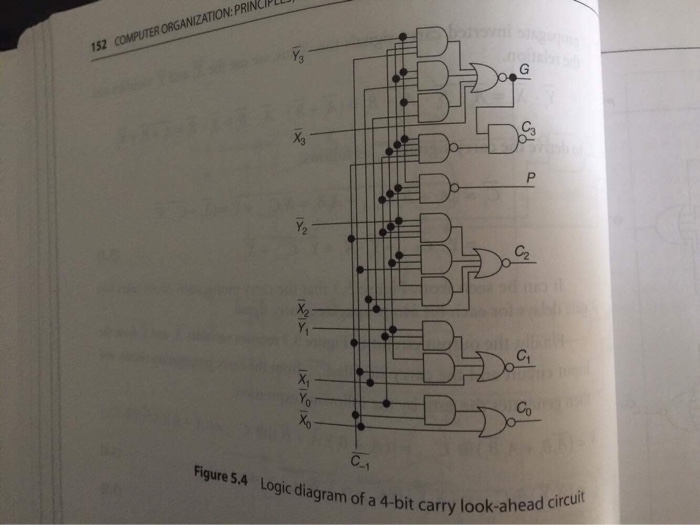

3) In a 4-bit carry-look-ahead adder using a carry-look-ahead circuit as shown in Figure 5.4, assume the same gate delays as in (2). What is the earliest time this 4-bit carry-look-ahead adder can be sure of a valid summation output? Explain how you reached your answer and how you did your calculations.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started