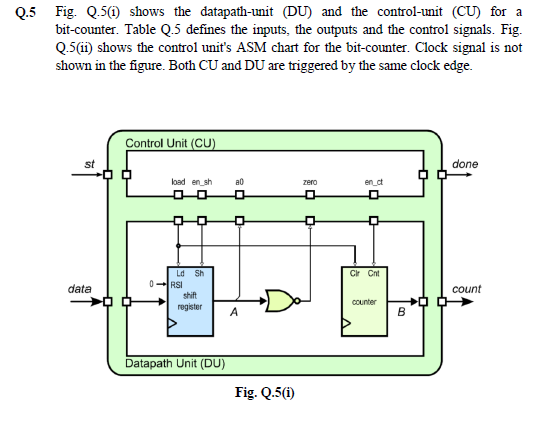

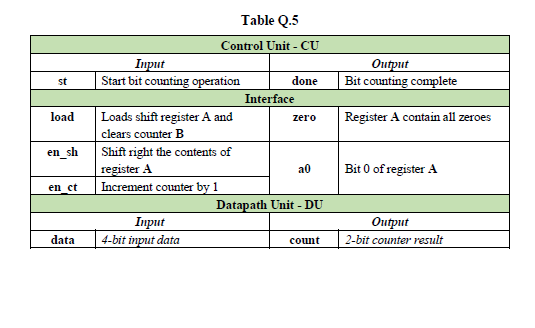

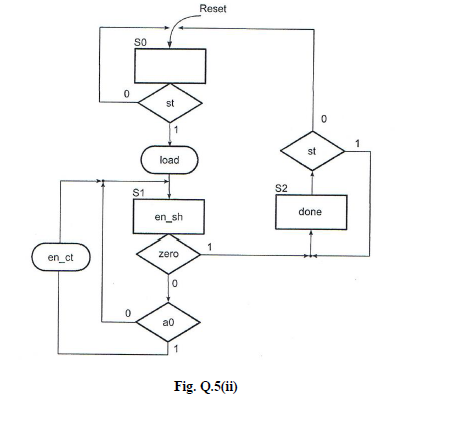

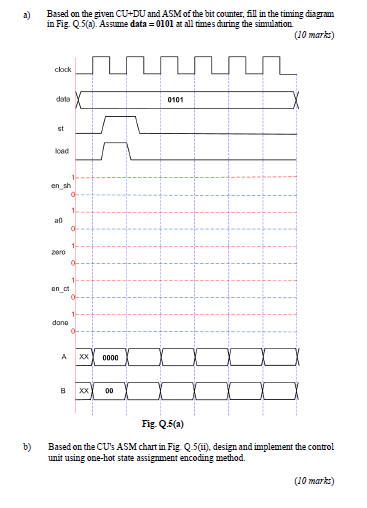

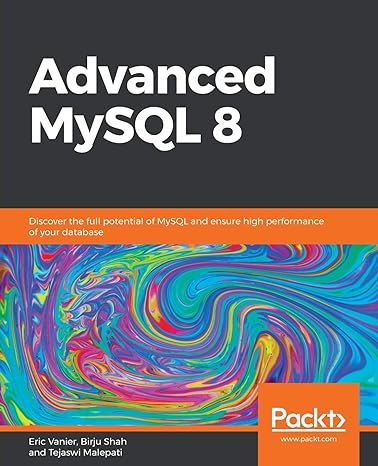

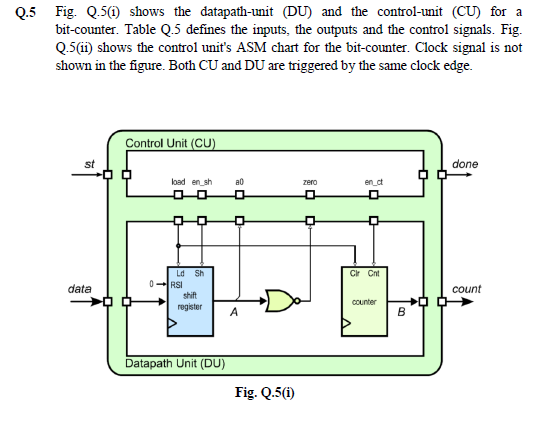

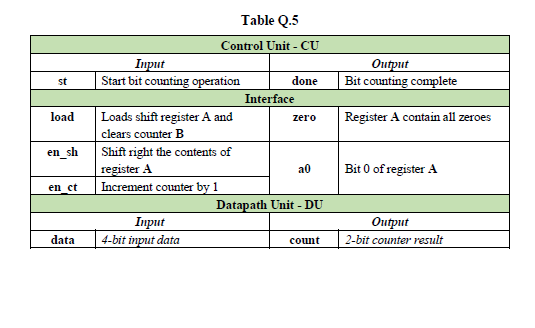

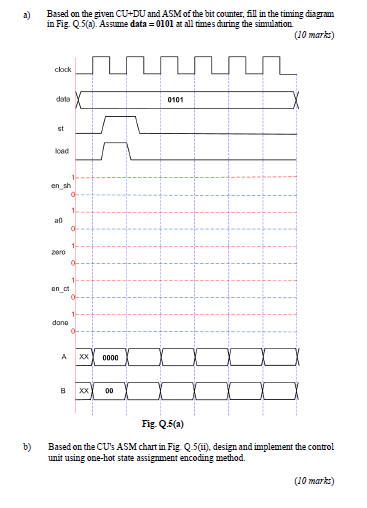

Q.5 Fig. 2.5(1) shows the datapath-unit (DU) and the control-unit (CU) for a bit-counter. Table Q.5 defines the inputs, the outputs and the control signals. Fig. Q.5(11) shows the control unit's ASM chart for the bit-counter. Clock signal is not shown in the figure. Both CU and DU are triggered by the same clock edge. Control Unit (CU) st done al load en_sh 00 zero O ent D 0 0 O Ld Sh Cir Cnt 0 RSI data count shift register counter B Datapath Unit (DU) Fig. Q.5(i) Output Bit counting complete st load Register A contain all zeroes Table 2.5 Control Unit - CU Input Start bit counting operation done Interface Loads shift register A and zero clears counter B Shift right the contents of register A a0 Increment counter by 1 Datapath Unit - DU Input 4-bit input data count en_sh Bit 0 of register A en ct Output 2-bit counter result data Reset SO 0 st 0 st load S1 S2 done en_sh 1 en_ct zero 0 0 ao Fig. Q.5(ii) a) Based on the given CU+DU and ASM of the bit counter, fill in the timing diagram in Fig. 25(a). Assume data = 0101 at all times during the simulation (10 marks) clock data 0101 st load en sh ab enot done A XX 0000 B 00 Fig. Q.5(a) b) Based on the CU'S ASM chart in Fig. Q5 (11) design and implement the control unit using one-hot state assignment encoding method. (10 marks) Q.5 Fig. 2.5(1) shows the datapath-unit (DU) and the control-unit (CU) for a bit-counter. Table Q.5 defines the inputs, the outputs and the control signals. Fig. Q.5(11) shows the control unit's ASM chart for the bit-counter. Clock signal is not shown in the figure. Both CU and DU are triggered by the same clock edge. Control Unit (CU) st done al load en_sh 00 zero O ent D 0 0 O Ld Sh Cir Cnt 0 RSI data count shift register counter B Datapath Unit (DU) Fig. Q.5(i) Output Bit counting complete st load Register A contain all zeroes Table 2.5 Control Unit - CU Input Start bit counting operation done Interface Loads shift register A and zero clears counter B Shift right the contents of register A a0 Increment counter by 1 Datapath Unit - DU Input 4-bit input data count en_sh Bit 0 of register A en ct Output 2-bit counter result data Reset SO 0 st 0 st load S1 S2 done en_sh 1 en_ct zero 0 0 ao Fig. Q.5(ii) a) Based on the given CU+DU and ASM of the bit counter, fill in the timing diagram in Fig. 25(a). Assume data = 0101 at all times during the simulation (10 marks) clock data 0101 st load en sh ab enot done A XX 0000 B 00 Fig. Q.5(a) b) Based on the CU'S ASM chart in Fig. Q5 (11) design and implement the control unit using one-hot state assignment encoding method. (10 marks)