Question 1 (3 points) Which of the following flip-flop timing parameters indicates the time it takes a Q output to respond to an input? Question

Question 1 (3 points)

Which of the following flip-flop timing parameters indicates the time it takes a Q output to respond to an input?

Question 1 options:

| tw(1), tw(h) | |

| fmax | |

| ts, th | |

| tphl, tplh |

Save

Question 2 (3 points)

Asynchronous flip-flop preset and clear inputs generally:

Question 2 options:

| cause the outputs to change states depending on the SR, JK, or similar controlling inputs. | |

| cause the outputs to change states as soon as the input clock makes the desired transition. | |

| clear the inputs so the flip-flop can start over. | |

| act as manual overrides that cause the outputs to change states regardless of the inputs or clock transitions. |

Save

Question 3 (3 points)

The setup time of a clocked flip-flop is:

Question 3 options:

| the maximum amount of time that an output must remain stable after an active clock transition. | |

| the minimum amount of time that an output must remain stable before an active clock transition. | |

| the minimum amount of time that an input must remain stable before an active clock transition. | |

| the minimum amount of time that an input must remain stable after an active clock transition. |

Save

Question 4 (3 points)

The symbol for a flip flop has a small triangle - and no bubble - on its clock (CLK) input. The triangle indicates:

Question 4 options:

| the FF is level active and can only change states when the CLOCK = 1. | |

| the FF is edge-triggered and can only change states when the clock goes from 1 to 0. | |

| the FF is an active LOW device and can only change states when the CLOCK = 0. | |

| the FF is edge-triggered and can only change states when the clock goes 0 to 1. |

Save

Question 5 (3 points)

A negative-edge-triggered J-K flip-flop is presently in the CLEAR state. Which of the following input conditions will cause it to change states?

Note:

PGT: Clock transition from '0' to '1'

NGT: Clock transition from '1' to '0'

Question 5 options:

| CLK = PGT, J = 1, and K = 0 | |

| CLK = PGT, J = O, and K = 1 | |

| CLK = NGT, J = O, and K = 1 | |

| CLK = NGT, J = 1, and K = 0 |

Save

Question 6 (3 points)

The difference between a D-latch and an edge-triggered D-type flip-flop is that the latch:

Question 6 options:

| always "latches" the Q output to the D input regardless of other inputs. | |

| is controlled by the logic level at its ENABLE input rather than a CLK transition. | |

| always "latches" the Q output to the complement of the D input regardless of other inputs. | |

| triggers on either the rising or falling edge of an ENABLE signal rather than the CLK input logic level. |

Save

Question 7 (3 points)

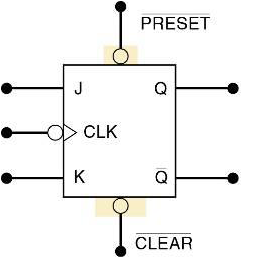

The preset and clear inputs to a J-K flip-flop are HIGH (1). Which of the following is true?

Question 7 options:

| The Q output is immediately set to 1. | |

| The flip-flop is free to respond to its J, K, and clock inputs. | |

| The Q output is in an ambiguous state. | |

| The Q output is immediately cleared. |

Save

Question 8 (3 points)

What is one disadvantage of an R-S flip-flop?

Question 8 options:

| It has no Enable input. | |

| It has only a single output. | |

| It has an invalid state. | |

| It has no CLOCK input. |

Save

Question 9 (3 points)

If both inputs of an S-R flip-flop are low, what will happen when the clock goes high?

Question 9 options:

| An invalid state will exist. | |

| No change will occur in the output. | |

| The output will reset. | |

| The output will toggle. |

Save

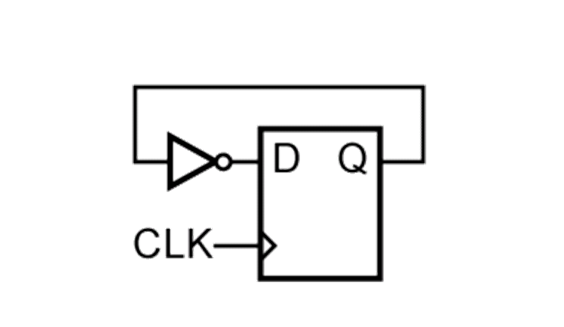

Question 10 (4 points)

Suppose that the in the circuit above the propagation delay of the inverter is 1.5 ns and the propagation delay and settup times of the flip-flop are 3.5 ns and 2 ns respectively. What is the shortest clock period for the circuit that will not violate the time constraints?

Question 10 options:

| 3.5 ns | |

| 5.5 ns | |

| 8 ns | |

| None of the above |

Save

Question 11 (3 points)

When both inputs of a J-K pulse-triggered FF are high, and the clock cycles, the output will ________.

Question 11 options:

| be invalid | |

| remain unchanged | |

| not change | |

| toggle |

Save

Question 12 (3 points)

What would be the output of a JK Flip-Flop (assume 74LS112) at the end if J=1 and K=0 for one clock pulse and then J=1 and K=1 for the next 3 clock pulses? Assume that PS and CLR are both 1.

Question 12 options:

| 0 | |

| 1 |

Save

Question 13 (5 points)

The figure above shows a S-R circuit and the the corresponding waveform for the inputs S and R. What are the values of the output Q for times t1, t2, t3 and t4 respectively?

Question 13 options:

| 0,1,1,0 | |

| 1,0,0,1 | |

| 1,1,0,0 | |

| 0,0,1,1 |

Save

Question 14 (5 points)

For the circuit of the figure above, if the circuit is fed with the waveform given, what are the values of Q for times t1,t2 and t3 respectively?

Question 14 options:

| |||

| |||

| |||

|

|

| |

| First, find the excitation equation for the Flip-Flop input D in function of Q and input. Then build the truth table using the inputs Q and "input" and find the output Q+. | |

Save

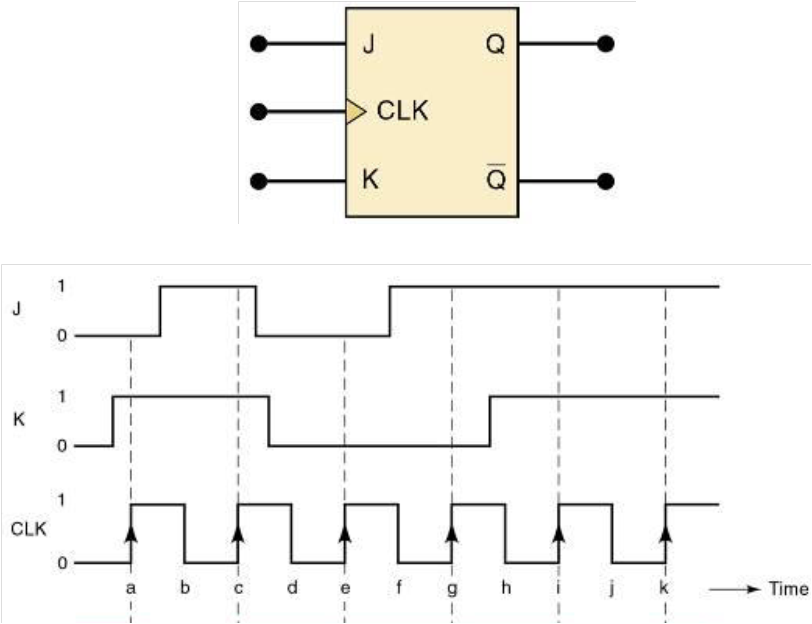

Question 15 (3 points)

The figure above shows a waveform for the inputs of a JK flip-flop rise-edge-triggering. What are the values of the flip-flop output for the times shown in b,d,f,h and j respectively?

Question 15 options:

| 0, 1, 0, 1, 1 | |

| 0, 1, 1, 1, 0 | |

| 0, 0, 1, 1, 0 | |

| Nonoe of the above |

Save

Question 16 (5 points)

The figure above shows a waveform for the inputs of a JK flip-flop falling-edge-triggering with PRESET and CLEAR. What are the values of the flip-flop output for the times shown in c, g, i, k and o respectively?

Question 16 options:

| 0, 0, 1, 1, 1 | |

| 0, 1, 1, 1, 0 | |

| 0, 1, 1, 0, 1 | |

| None of the above |

Save

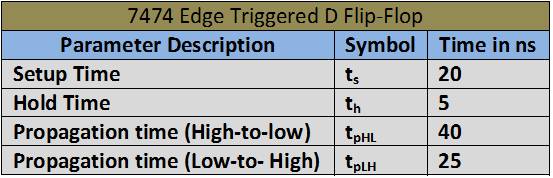

Question 17 (3 points)

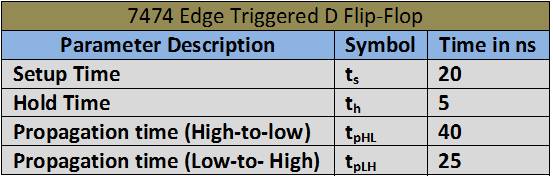

The table given above shows some parameters for the a 7474 Edge Triggered D Flip-Flop. Which of the following circuit parameters would be most likely to limit the maximum operating frequencythis type of flip-flop?

Question 17 options:

| Low-to-High Propagation delay time | |

| High-to-Low Propagation delay time | |

| Set-up time | |

| Hold time |

Save

Question 18 (3 points)

The table given above shows some parameters for the a 7474 Edge Triggered D Flip-Flop. What would be the maximum operating frequency this type of flip-flop?

Question 18 options:

| 15.38 MHz | |

| 16.66 MHz | |

| 22.22 MHz | |

| 40 MHz |

|

| |

|

| |

Save

Question 19 (3 points)

For the circuit shown what are the values of Q for times t0,t1,t2 respectively?

Assume Q=0 initially.

Question 19 options:

| 1 1 1 | |

| 0 0 0 | |

| 0 1 0 | |

| 0 0 1 | |

| None of the above |

Step by Step Solution

There are 3 Steps involved in it

Step: 1

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started

Hide hint for Question 14

Hide hint for Question 14