Question: Question 1 (a) [4%) You are provided with an extract from the Multisim PLD datasheet for the CNTR_4_BIN_S 4-bit binary counter () The third paragraph

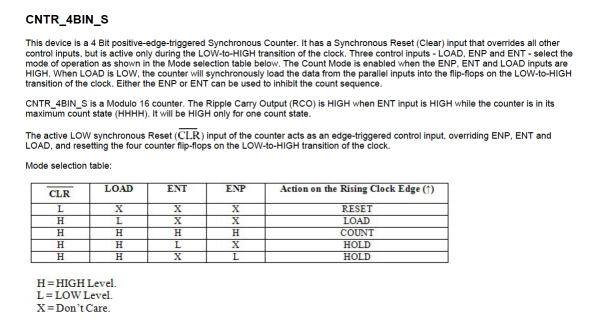

Question 1 (a) [4%) You are provided with an extract from the Multisim PLD datasheet for the CNTR_4_BIN_S 4-bit binary counter () The third paragraph of the extract says that the CLR input is an edge-triggered control input. Explain what this means in your own words, and state explicitly how the inputs to the counter must be used in order to clear the four bits. (ii) The mode selection table confirms the behaviour of the CLR input. Explain where in the table this information appears and how it confirms the stated behaviour. [4%) (b) [8%) A demultiplexer implements in some sense the opposite' function to a multiplexer. Explain what a demultiplexer does, using as an example the case which is opposite to a 16-to-1 multiplexer. Include a list of the inputs and outputs which would be found on a typical demultiplexer, and make clear the function of each. [6%) (c) The Xilinx Artix-7 FPGA that you used in the laboratory has a volatile configuration (that is, the configuration is lost when power is removed from the chip). You loaded your designs into the FPGA over a serial link from a computer, but this is obviously not a suitable method for an FPGA built into an embedded system, as for example, in a circuit board on an aircraft. How else can the FPGA be configured with a circuit? (Hint: this is how the built-in self-test circuit on the Basys3 board can be configured into the FPGA.) (d) In the laboratory, your designs were represented as schematics, and exported to VHDL [6%) code for transfer to Xilinx Vivado. Neither the schematics nor the VHDL code included pin numbers for the signals which were to pass in or out of the FPGA. How was this information conveyed to Vivado to ensure that these signals were routed to the correct pins, and therefore to the correct traces on the Basys3 printed circuit board? [12%) (e) Block diagram thinking is important in the design of many electronic systems, but especially digital systems. Outline what the term means and explain how it relates to the concept of hierarchy. CNTR_4BIN_S This device is a 4 Bit positive-edge-triggered Synchronous Counter. It has a Synchronous Reset (Clear) input that overrides all other control inputs, but is active only during the LOW-to-HIGH transition of the clock. Three control inputs -LOAD, ENP and ENT - Select the mode of operation as shown in the Mode selection table below. The Count Mode is enabled when the ENP, ENT and LOAD inputs are HIGH. When LOAD is LOW, the counter will synchronously load the data from the parallel inputs into the flip-flops on the LOW-to-HIGH transition of the clock. Either the ENP or ENT can be used to inhibit the count sequence. CNTR_4BIN_S is a Modulo 16 counter. The Ripple Carry Output (RCO) is HIGH when ENT input is HIGH while the counter is in its maximum count state (HHHH). It will be HIGH only for one count state. The active LOW synchronous Reset (CLR) input of the counter acts as an edge-triggered control input, overriding ENP, ENT and LOAD, and resetting the four counter flip-flops on the LOW-o-HIGH transition of the clock. Mode selection table: LOAD ENT ENP Action on the Rising Clock Edge (1) X CLR L H H H H L H H H H L H L RESET LOAD COUNT HOLD HOLD H=HIGH Level L = LOW Level X=Don't Care. Question 1 (a) [4%) You are provided with an extract from the Multisim PLD datasheet for the CNTR_4_BIN_S 4-bit binary counter () The third paragraph of the extract says that the CLR input is an edge-triggered control input. Explain what this means in your own words, and state explicitly how the inputs to the counter must be used in order to clear the four bits. (ii) The mode selection table confirms the behaviour of the CLR input. Explain where in the table this information appears and how it confirms the stated behaviour. [4%) (b) [8%) A demultiplexer implements in some sense the opposite' function to a multiplexer. Explain what a demultiplexer does, using as an example the case which is opposite to a 16-to-1 multiplexer. Include a list of the inputs and outputs which would be found on a typical demultiplexer, and make clear the function of each. [6%) (c) The Xilinx Artix-7 FPGA that you used in the laboratory has a volatile configuration (that is, the configuration is lost when power is removed from the chip). You loaded your designs into the FPGA over a serial link from a computer, but this is obviously not a suitable method for an FPGA built into an embedded system, as for example, in a circuit board on an aircraft. How else can the FPGA be configured with a circuit? (Hint: this is how the built-in self-test circuit on the Basys3 board can be configured into the FPGA.) (d) In the laboratory, your designs were represented as schematics, and exported to VHDL [6%) code for transfer to Xilinx Vivado. Neither the schematics nor the VHDL code included pin numbers for the signals which were to pass in or out of the FPGA. How was this information conveyed to Vivado to ensure that these signals were routed to the correct pins, and therefore to the correct traces on the Basys3 printed circuit board? [12%) (e) Block diagram thinking is important in the design of many electronic systems, but especially digital systems. Outline what the term means and explain how it relates to the concept of hierarchy. CNTR_4BIN_S This device is a 4 Bit positive-edge-triggered Synchronous Counter. It has a Synchronous Reset (Clear) input that overrides all other control inputs, but is active only during the LOW-to-HIGH transition of the clock. Three control inputs -LOAD, ENP and ENT - Select the mode of operation as shown in the Mode selection table below. The Count Mode is enabled when the ENP, ENT and LOAD inputs are HIGH. When LOAD is LOW, the counter will synchronously load the data from the parallel inputs into the flip-flops on the LOW-to-HIGH transition of the clock. Either the ENP or ENT can be used to inhibit the count sequence. CNTR_4BIN_S is a Modulo 16 counter. The Ripple Carry Output (RCO) is HIGH when ENT input is HIGH while the counter is in its maximum count state (HHHH). It will be HIGH only for one count state. The active LOW synchronous Reset (CLR) input of the counter acts as an edge-triggered control input, overriding ENP, ENT and LOAD, and resetting the four counter flip-flops on the LOW-o-HIGH transition of the clock. Mode selection table: LOAD ENT ENP Action on the Rising Clock Edge (1) X CLR L H H H H L H H H H L H L RESET LOAD COUNT HOLD HOLD H=HIGH Level L = LOW Level X=Don't Care

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts