Answered step by step

Verified Expert Solution

Question

1 Approved Answer

QUESTION #1 PLEASE Propagation Delay for the 1-bit Full Adder Recall from class that the basic building blocks for addition circuits are defined by the

QUESTION #1 PLEASE

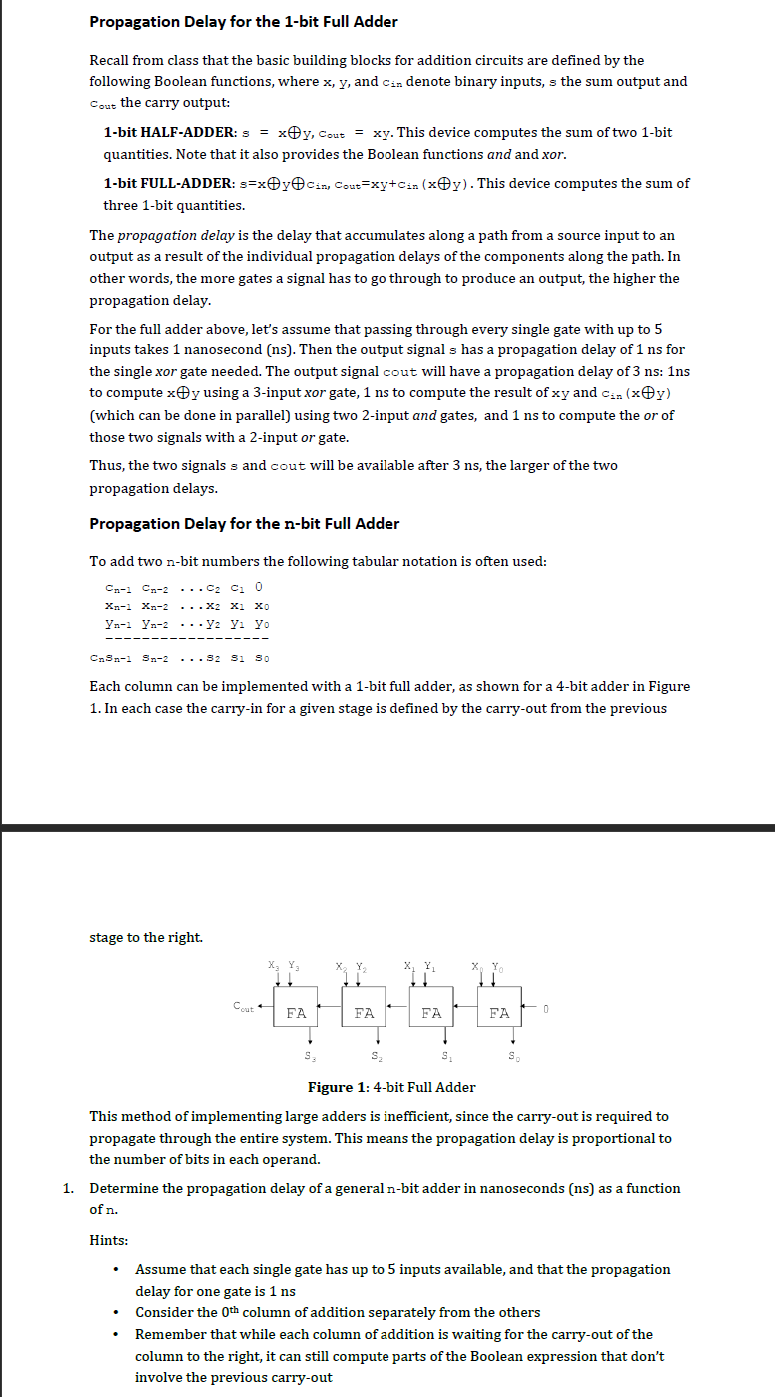

Propagation Delay for the 1-bit Full Adder Recall from class that the basic building blocks for addition circuits are defined by the following Boolean functions, where x, y, and Cin denote binary inputs, s the sum output and Cout the carry output: 1-bit HALF-ADDER: S = x y, Cout = xy. This device computes the sum of two 1-bit quantities. Note that it also provides the Boolean functions and and xor. 1-bit FULL-ADDER: s=xeycin, Cout=xy+cin (xOy). This device computes the sum of three 1-bit quantities. The propagation delay is the delay that accumulates along a path from a source input to an output as a result of the individual propagation delays of the components along the path. In other words, the more gates a signal has to go through to produce an output, the higher the propagation delay. For the full adder above, let's assume that passing through every single gate with up to 5 inputs takes 1 nanosecond (ns). Then the output signal s has a propagation delay of 1 ns for the single xor gate needed. The output signal cout will have a propagation delay of 3 ns: Ins to compute x y using a 3-input xor gate, 1 ns to compute the result of xy and can (x@y) (which can be done in parallel) using two 2-input and gates, and 1 ns to compute the or of those two signals with a 2-input or gate. Thus, the two signals s and cout will be available after 3 ns, the larger of the two propagation delays. Propagation Delay for the n-bit Full Adder To add two n-bit numbers the following tabular notation is often used: Ca-i Cn-2 ...C2 C 0 Xn-1 X.-2 ...X2 X. Xo Yn-i Yn-2 ... 42 y. Yo Casn-i S.-2 ...32 3. So Each column can be implemented with a 1-bit full adder, as shown for a 4-bit adder in Figure 1. In each case the carry-in for a given stage is defined by the carry out from the previous stage to the right Pout 4 FA FA FA A FA S So Figure 1: 4-bit Full Adder This method of implementing large adders is inefficient, since the carry-out is required to propagate through the entire system. This means the propagation delay is proportional to the number of bits in each operand. 1. Determine the propagation delay of a general n-bit adder in nanoseconds (ns) as a function of n. Hints: Assume that each single gate has up to 5 inputs available, and that the propagation delay for one gate is 1 ns Consider the oth column of addition separately from the others Remember that while each column of addition is waiting for the carry-out of the column to the right, it can still compute parts of the Boolean expression that don't involve the previous carry-outStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started