Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Question 2 (5 points each, total 20 points) The goal is to design a synchronous, 4-bit (modulo 16), reversible (up and down), binary counter with

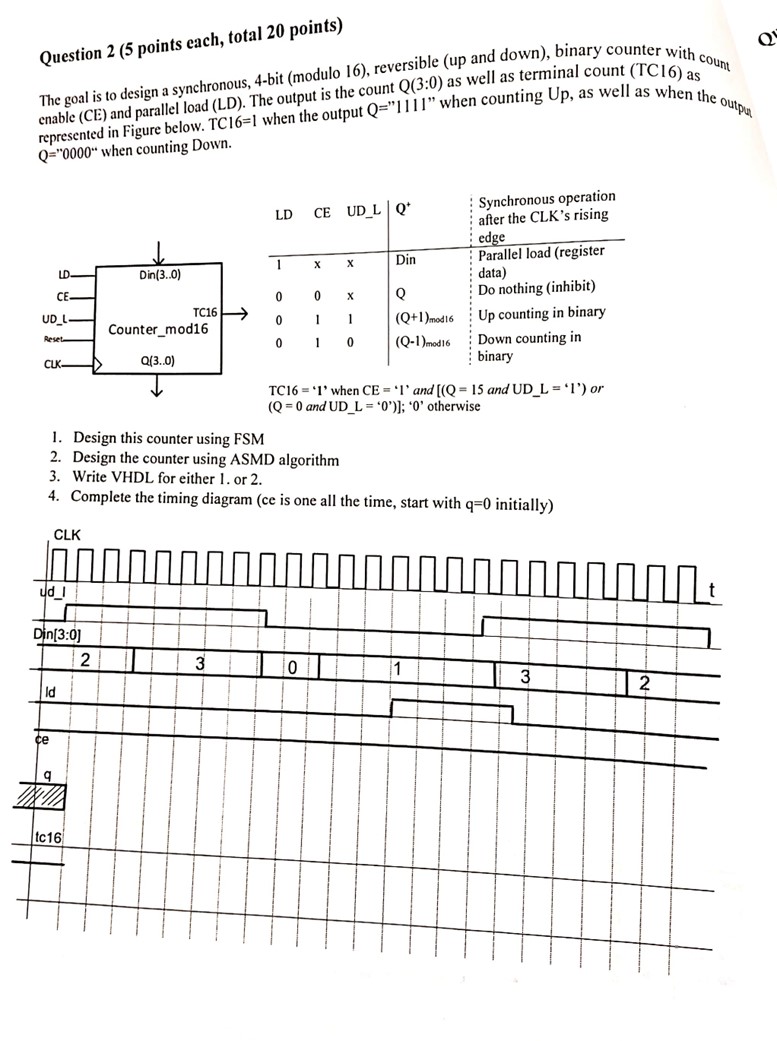

Question 2 (5 points each, total 20 points) The goal is to design a synchronous, 4-bit (modulo 16), reversible (up and down), binary counter with count enable (CE) and parallel load (LD). The output is the count Q(3:0) as well as terminal count (TCl6) as represented in Figure below. TC16=1 when the output Q="1111 " when counting Up, as well as when the Out puy Q="0000 " when counting Down. TC16= ' 1 ' when CE= ' 1 ' and [(Q=15 and UDL= ' 1 ') or (Q=0 and UDL= ' 0 ')]; ' 0 ' otherwise 1. Design this counter using FSM 2. Design the counter using ASMD algorithm 3. Write VHDL for either 1 . or 2 . 4. Complete the timing diagram (ce is one all the time, start with q=0 initially)

Question 2 (5 points each, total 20 points) The goal is to design a synchronous, 4-bit (modulo 16), reversible (up and down), binary counter with count enable (CE) and parallel load (LD). The output is the count Q(3:0) as well as terminal count (TCl6) as represented in Figure below. TC16=1 when the output Q="1111 " when counting Up, as well as when the Out puy Q="0000 " when counting Down. TC16= ' 1 ' when CE= ' 1 ' and [(Q=15 and UDL= ' 1 ') or (Q=0 and UDL= ' 0 ')]; ' 0 ' otherwise 1. Design this counter using FSM 2. Design the counter using ASMD algorithm 3. Write VHDL for either 1 . or 2 . 4. Complete the timing diagram (ce is one all the time, start with q=0 initially) Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started