Answered step by step

Verified Expert Solution

Question

1 Approved Answer

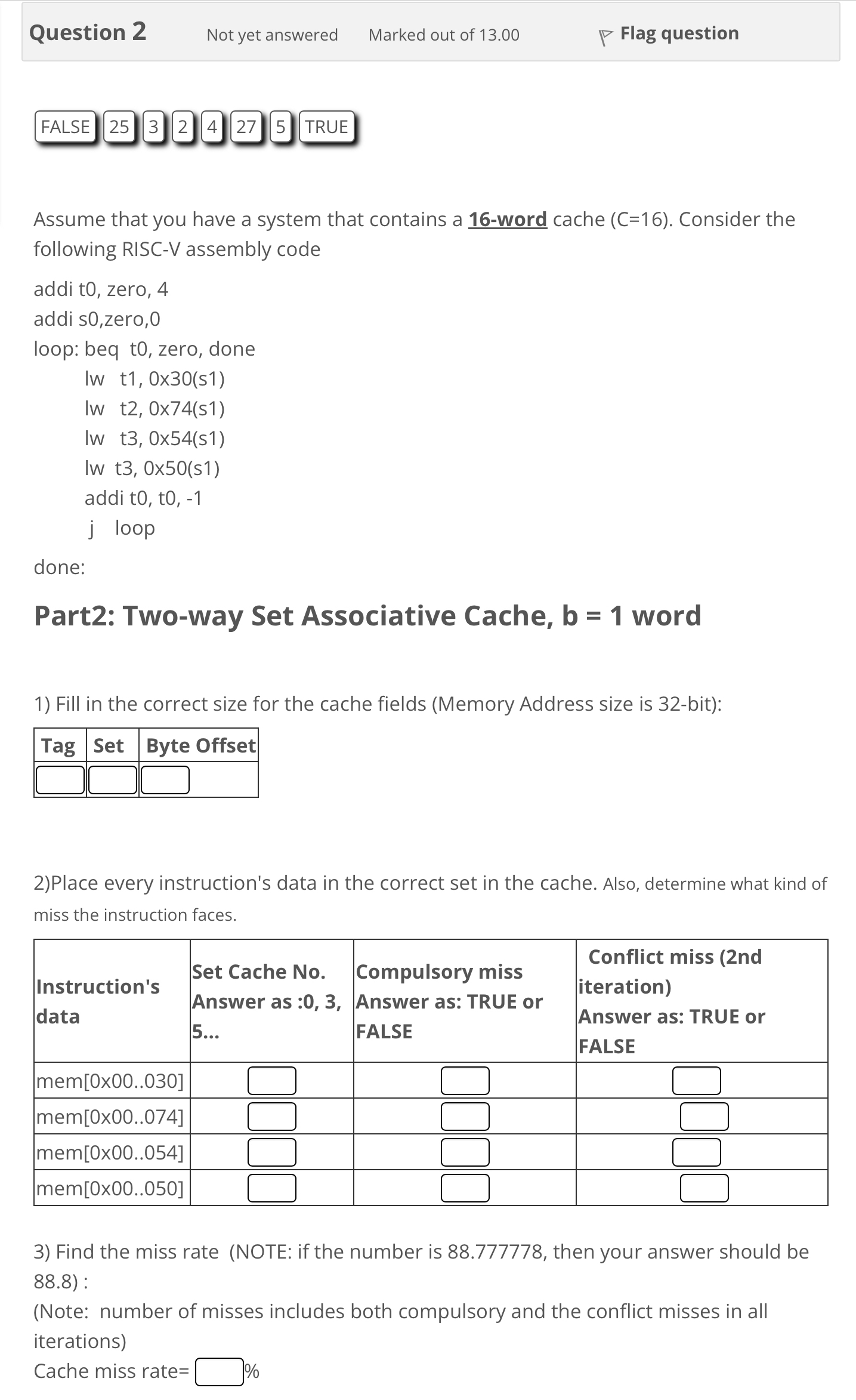

Question 2 Not yet answered Marked out of 1 3 . 0 0 Flag question FALSE 2 5 3 2 7 TRUE Assume that you

Question

Not yet answered

Marked out of

Flag question

FALSE TRUE

Assume that you have a system that contains a word cache Consider the following RISCV assembly code

addi t zero,

addi szero,

loop: beq t zero, done

addi

Ioop

done:

Part: Twoway Set Associative Cache, word

Fill in the correct size for the cache fields Memory Address size is bit:

tableTagSet,Byte Offset

Place every instruction's data in the correct set in the cache. Also, determine what kind of miss the instruction faces.

tabletableInstructionsdatatableSet Cache NoAnswer as :tableCompulsory missAnswer as: TRUE orFALSEtableConflict miss nditerationAnswer as: TRUE orFALSEmemxmemx

Find the miss rate NOTE: if the number is then your answer should be :

Note: number of misses includes both compulsory and the conflict misses in all iterations

Cache miss rate

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started