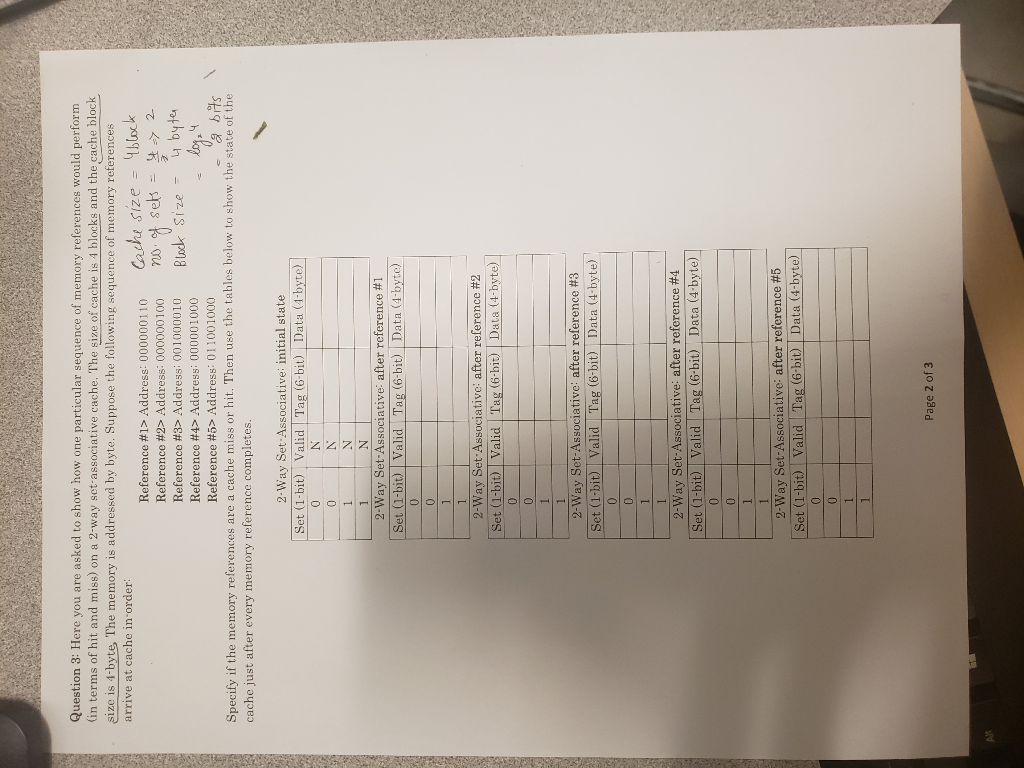

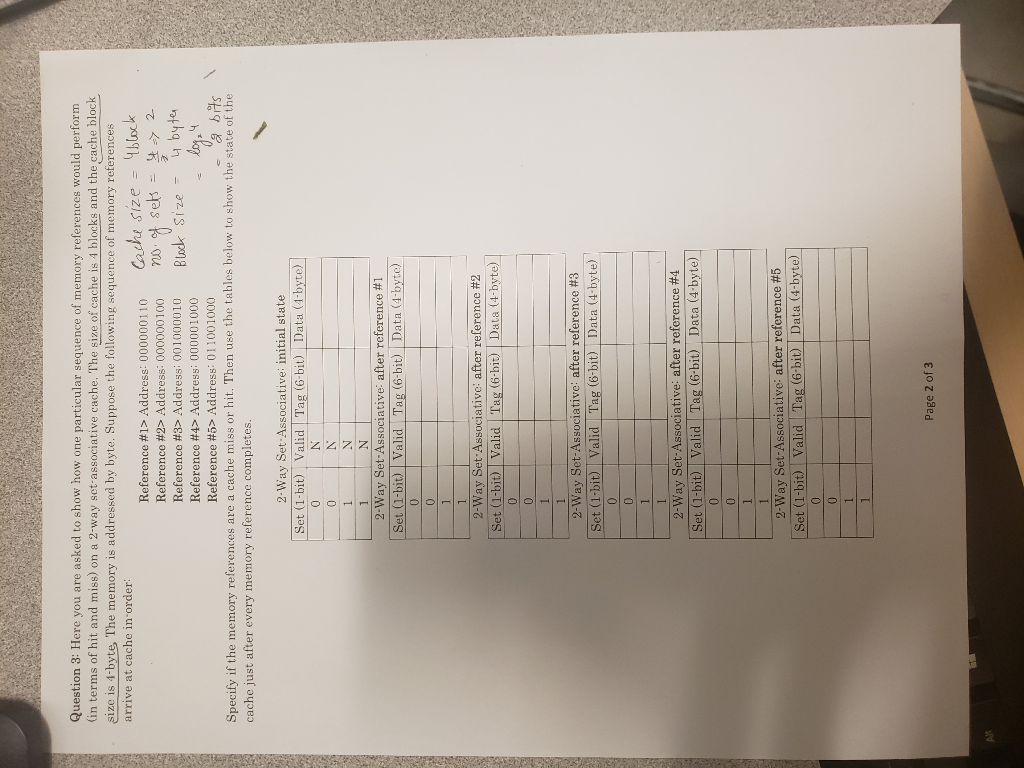

Question 3: Here you are asked to show how one particular sequence of memory references would perform (in terms of hit and miss) on a 2-way sct associative cache. The ize of cache is 4 blocks and the cache block size is 4-byte The memory is addressed by byte. Suppose the following sequence of memory references arrive at cache in order Cache size block u byte Reference #1> Address: 000000110 Reference #2> Address: 000000100 t set no Reference #3> Address: 001000010 Block Srze Reference #42 Address: 000001000 Reference #52 Address: 01 1001000 Specify if the memory references are a cache miss or hit. Then use the tables below to show the state of the cache just after every memory reference completes. 2-Way Set Associative: initial state Set (1-bit) Valid Tag (6bit) Data (1-byte 2-way Set-Associative-after reference #1 Set (1-bit) Valid Tag (6bit) Data (4-byte 2-way Set-Associative: after reference #2 Set (1-bit) Valid Tag (6-bit) Data (4-byte) 2-way Set-Associative: after reference #3 Set (1-bit Valid Tag (6-bit) Data (4-byte 2-Way Set-Associative after reference #4 Set (1-bit) Valid Tag (6-bit) Data (4-byte) 2-Way Set-Associative, after reference #5 Set (1-bit) Valid Tag (6-bit) Data (4-byte Page 2 of 3 An Question 3: Here you are asked to show how one particular sequence of memory references would perform (in terms of hit and miss) on a 2-way sct associative cache. The ize of cache is 4 blocks and the cache block size is 4-byte The memory is addressed by byte. Suppose the following sequence of memory references arrive at cache in order Cache size block u byte Reference #1> Address: 000000110 Reference #2> Address: 000000100 t set no Reference #3> Address: 001000010 Block Srze Reference #42 Address: 000001000 Reference #52 Address: 01 1001000 Specify if the memory references are a cache miss or hit. Then use the tables below to show the state of the cache just after every memory reference completes. 2-Way Set Associative: initial state Set (1-bit) Valid Tag (6bit) Data (1-byte 2-way Set-Associative-after reference #1 Set (1-bit) Valid Tag (6bit) Data (4-byte 2-way Set-Associative: after reference #2 Set (1-bit) Valid Tag (6-bit) Data (4-byte) 2-way Set-Associative: after reference #3 Set (1-bit Valid Tag (6-bit) Data (4-byte 2-Way Set-Associative after reference #4 Set (1-bit) Valid Tag (6-bit) Data (4-byte) 2-Way Set-Associative, after reference #5 Set (1-bit) Valid Tag (6-bit) Data (4-byte Page 2 of 3 An