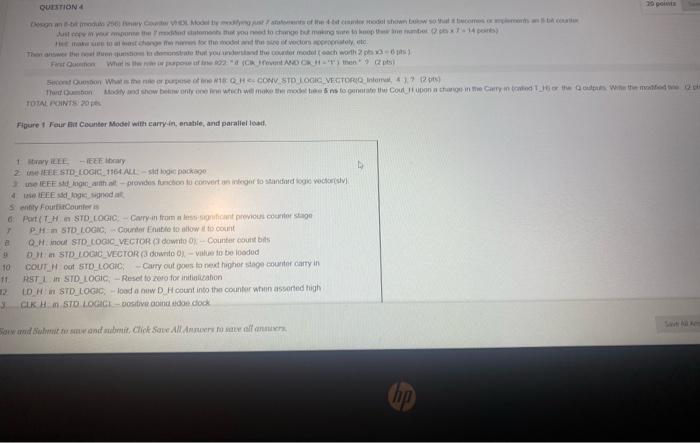

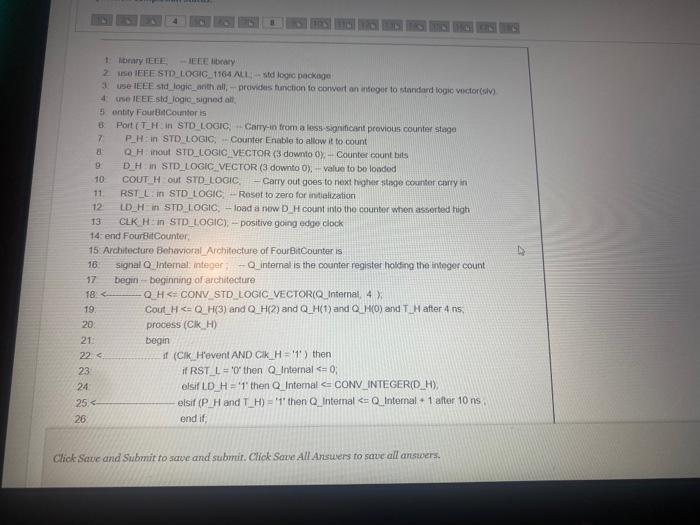

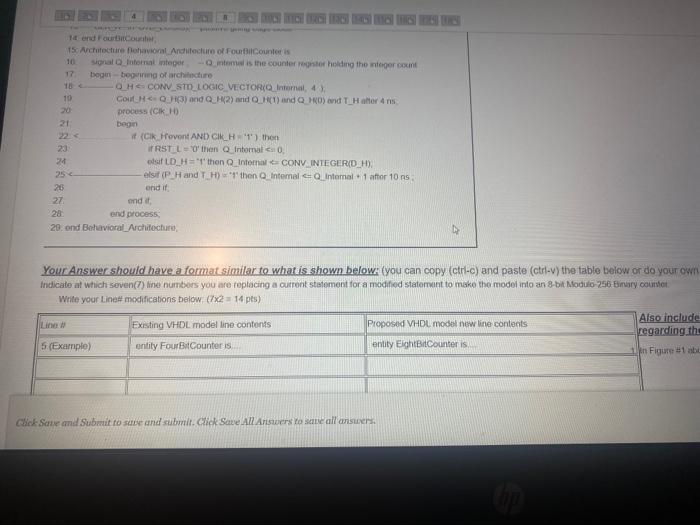

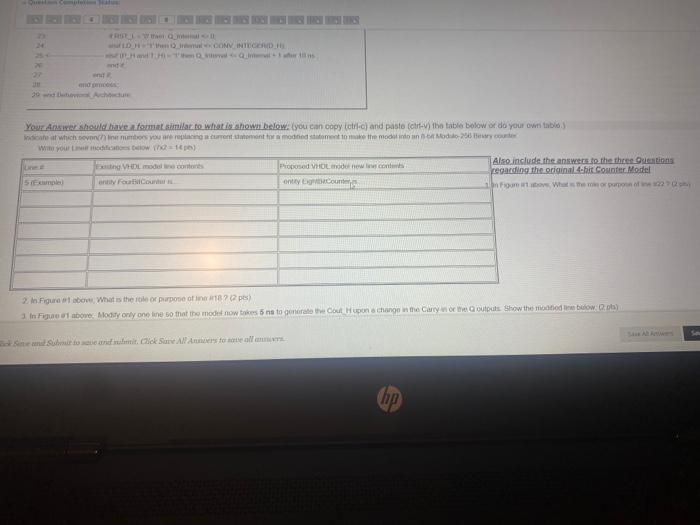

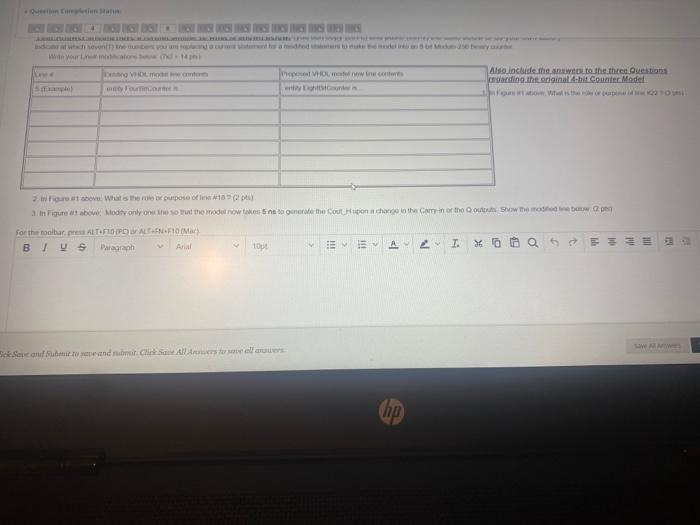

QUESTION 4 70 son Model Sitio med tomato change man wat op 14 ) to change with mode odontolat Then there that you understand the modelach worth 2011 First What is pod DOH) then Sot Osbon What is there are 1 H CONV STO LOGIC VECTOR into 120) The And show bewonin ech will make the mins to get out on the in the carrying With TOTAL POINTS 20 Figure 1 Fourt Counter Model with carry.in, enable, and parallel load, 1 LIL -Bay 2 EESTO LOGIC, 1164 AL slog package IEEE Sht-provides function to converting to standard logo vector 4 IEEE Ingicida Senty Four Counters Port LH in STD LOGIC Carry.in from the previous counter stage PH STD LOGIC, Counter Cable to allow to count B Hinou! STD LOGIC_VECTOR down Counter counts STD LOGIC VECTOR ( dowloo value to be loaded 10 COUT N Out STO LOGIC -Carry out goes to next higher stage counter carryin 11 RST LIN STD LOGIC - Reset to 10 for initialcahon LD STD_LOGIC, -load new D. Hount into the counter when assorted high CLK HM STD LOGICE-OS in de dock Sawer window Chok Sare All Arrow alfa 1 IEEE IEEE library 2 IEEE STD_LOGIC 1164 ALL logic package Use IEEE std logie_anth all-provides function to convert an integer to standard logic vector(sv) 4 IEEE std_logic_signed all 5 entity Four BitCounter is 8 Port (T_Hin STD LOGIC -- Carry-in from a les significant previous counter stage 7 P_H in STD LOGIC - Counter Enable to allow it to count 3 Q Hout STD_LOGIC VECTOR (3 downto Oy - Counter count bits D_H STD LOGIC VECTOR (3 downto Oy value to be loaded 10 COUT H out STD LOGIC, Carry out goes to next higher stage counter carry in 11 RST_L in STD_LOGIC Roser to zero for initialization 12 LD_Hin STD LOGIC -- Ioad a new D H count into the counter when asserted high 13 CLK Hin STD_LOGIC). -- positive going edge clock 14-end FourBdCounter 15. Architecture Behavioral Architecture of Four BitCounter is 16 signal Internal integer Q_intemal is the counter register holding the integer count 17 begin beginning of architecture H 19 Cout_HQ_H(3) and Q H(2) and Q_H(1) and Q HO) and T Matter Ans 20 process (CIK H) 21 begin 22 if (Cik Hovent AND CK H='1') then 23 if RST L = ''then Q_Internal 19 Cout_HQ_H(3) and Q H(2) and Q_H(1) and Q HO) and T Matter Ans 20 process (CIK H) 21 begin 22 if (Cik Hovent AND CK H='1') then 23 if RST L = ''then Q_Internal