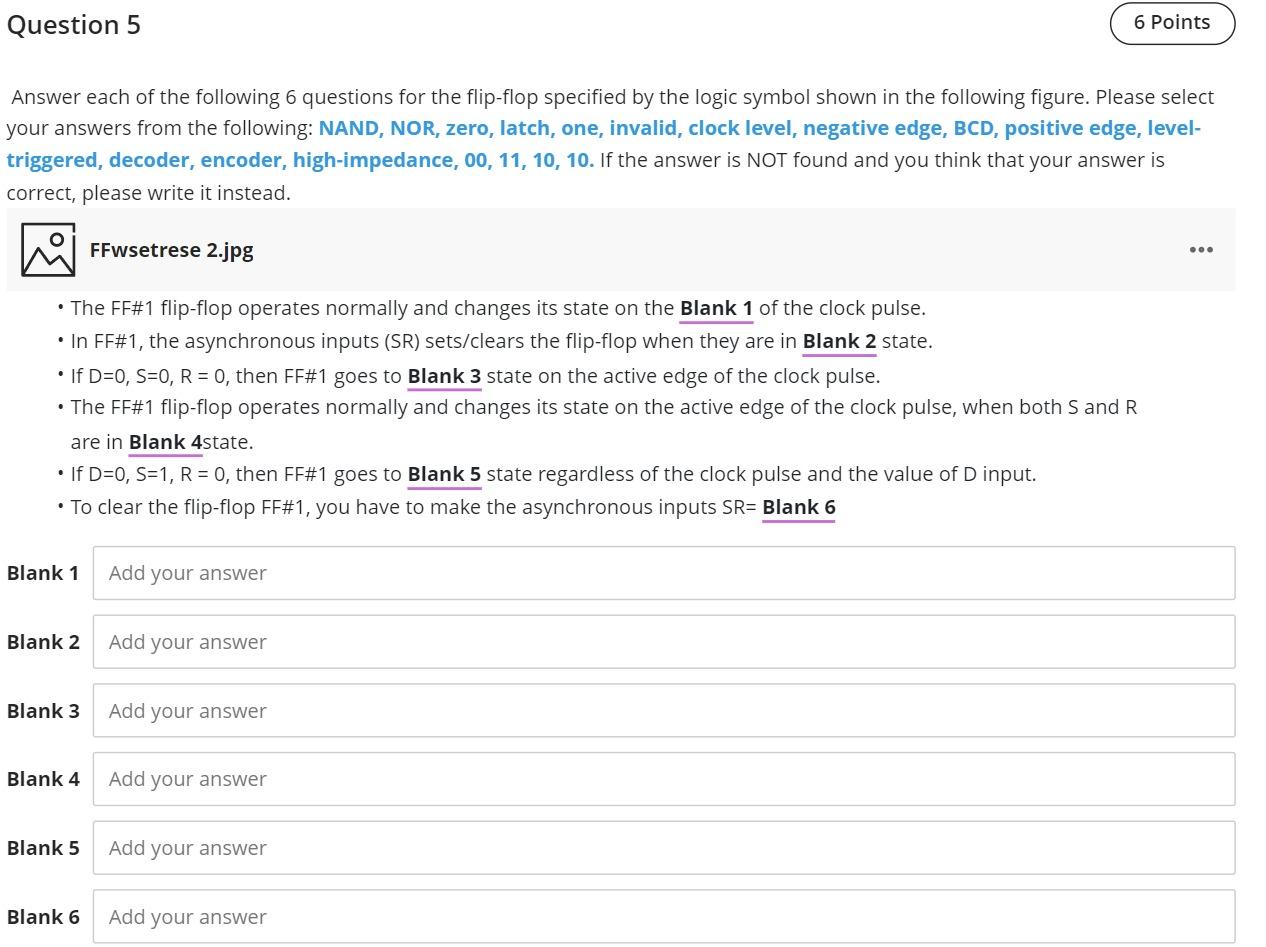

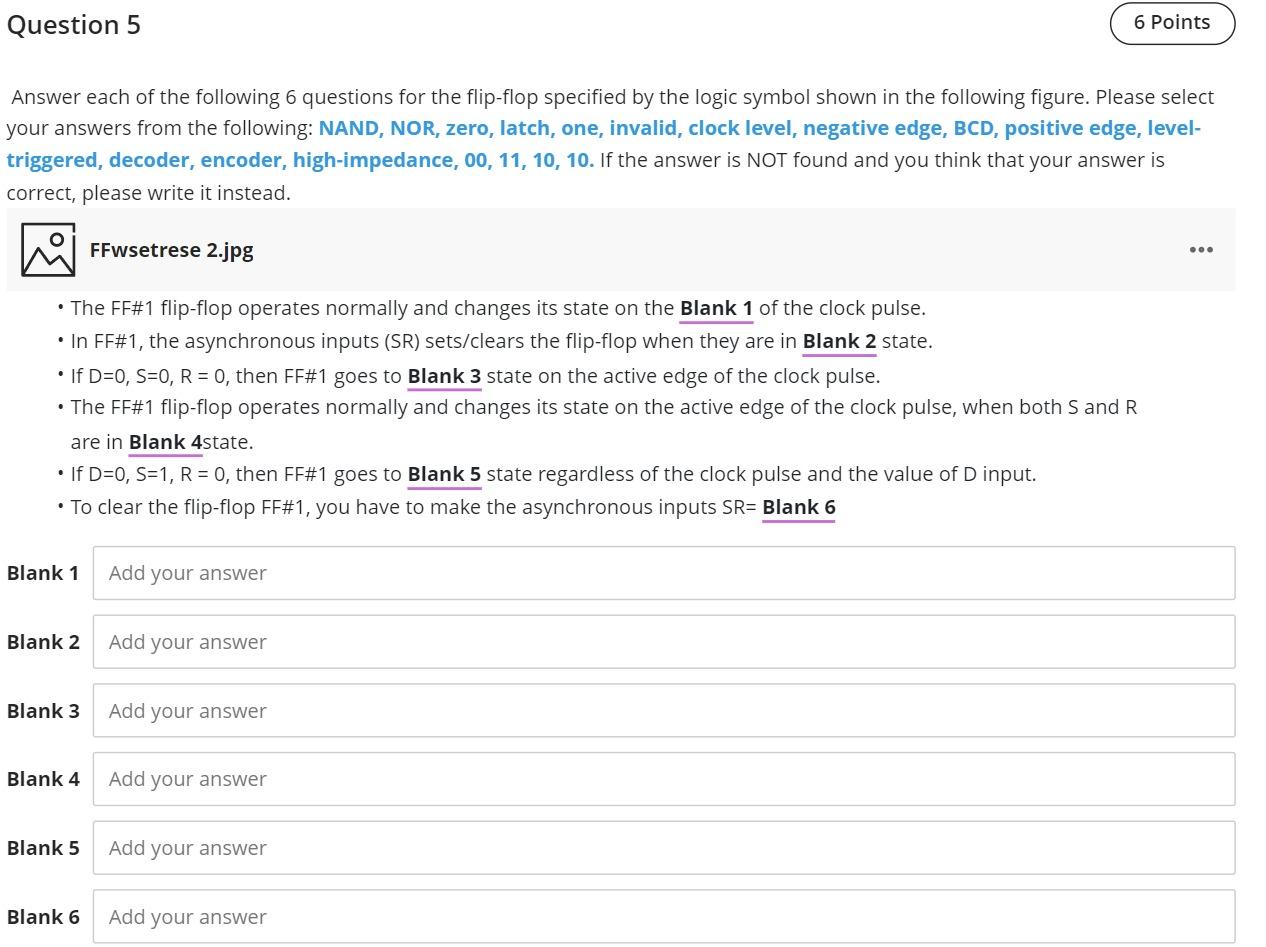

Question 5 6 Points Answer each of the following 6 questions for the flip-flop specified by the logic symbol shown in the following figure. Please select your answers from the following: NAND, NOR, zero, latch, one, invalid, clock level, negative edge, BCD, positive edge, level- triggered, decoder, encoder, high-impedance, 00, 11, 10, 10. If the answer is NOT found and you think that your answer is correct, please write it instead. FFwsetrese 2.jpg The FF#1 flip-flop operates normally and changes its state on the Blank 1 of the clock pulse. In FF#1, the asynchronous inputs (SR) sets/clears the flip-flop when they are in Blank 2 state. If D=0, S=0, R = 0, then FF#1 goes to Blank 3 state on the active edge of the clock pulse. The FF#1 flip-flop operates normally and changes its state on the active edge of the clock pulse, when both S and R are in Blank 4state. If D=0, S=1, R = 0, then FF#1 goes to Blank 5 state regardless of the clock pulse and the value of D input. To clear the flip-flop FF#1, you have to make the asynchronous inputs SR= Blank 6 . Blank 1 Add your answer Blank 2 Add your answer Blank 3 Add your answer Blank 4 Add your answer Blank 5 Add your answer Blank 6 Add your answer Question 5 6 Points Answer each of the following 6 questions for the flip-flop specified by the logic symbol shown in the following figure. Please select your answers from the following: NAND, NOR, zero, latch, one, invalid, clock level, negative edge, BCD, positive edge, level- triggered, decoder, encoder, high-impedance, 00, 11, 10, 10. If the answer is NOT found and you think that your answer is correct, please write it instead. FFwsetrese 2.jpg The FF#1 flip-flop operates normally and changes its state on the Blank 1 of the clock pulse. In FF#1, the asynchronous inputs (SR) sets/clears the flip-flop when they are in Blank 2 state. If D=0, S=0, R = 0, then FF#1 goes to Blank 3 state on the active edge of the clock pulse. The FF#1 flip-flop operates normally and changes its state on the active edge of the clock pulse, when both S and R are in Blank 4state. If D=0, S=1, R = 0, then FF#1 goes to Blank 5 state regardless of the clock pulse and the value of D input. To clear the flip-flop FF#1, you have to make the asynchronous inputs SR= Blank 6 . Blank 1 Add your answer Blank 2 Add your answer Blank 3 Add your answer Blank 4 Add your answer Blank 5 Add your answer Blank 6 Add your