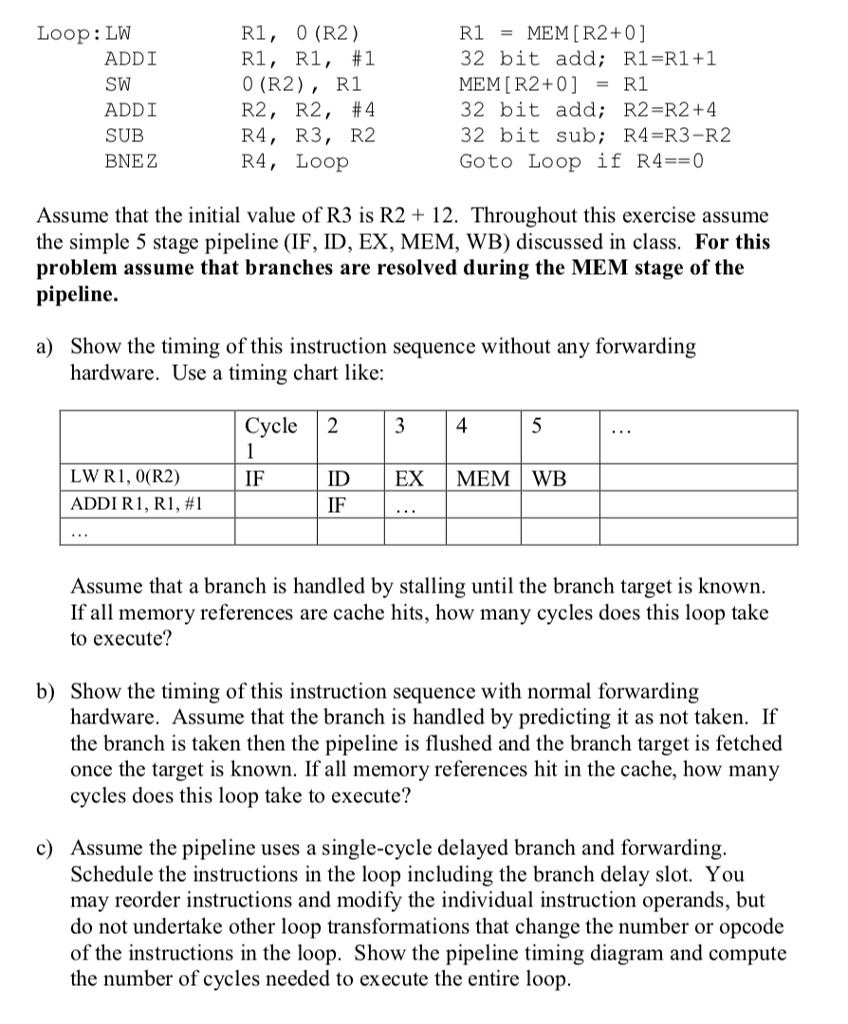

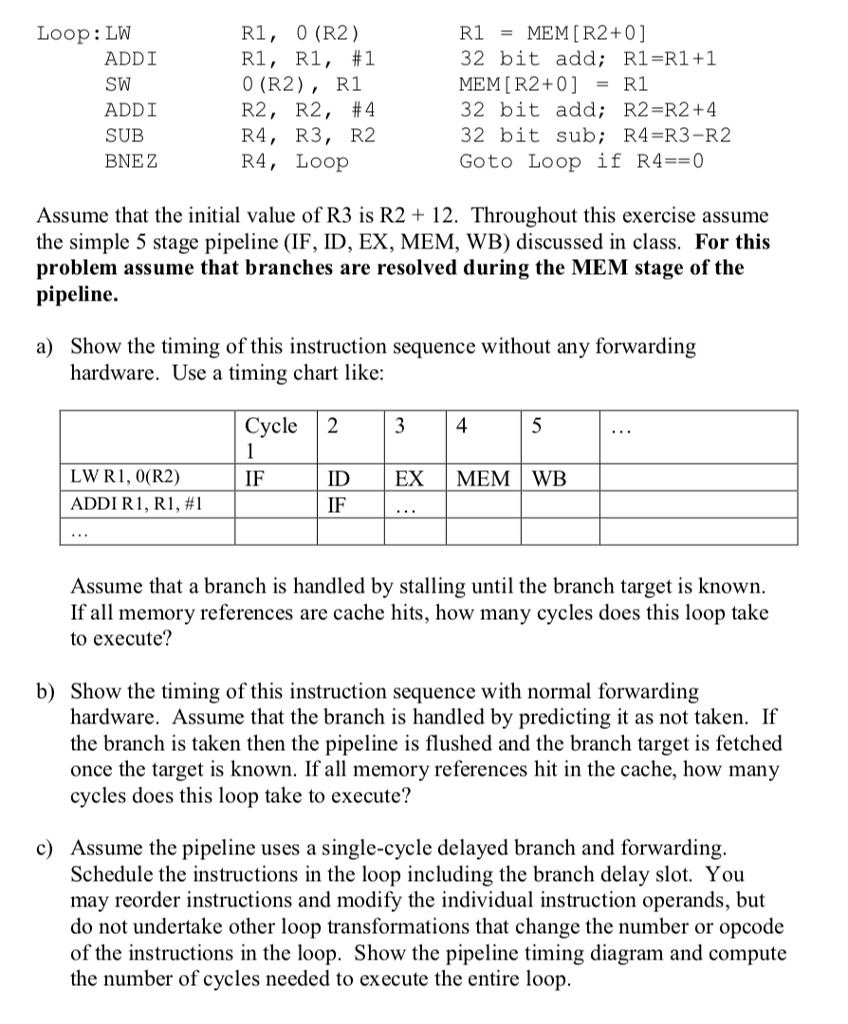

R1, 0 (R2) R1, R1, #1 0 (R2), R1 R2, R2, #4 R4, R3, R2 R4, Loop R1 = MEM [R2+0] 32 bit add; R1=R1+1 MEM [R2 + 0] = RI 32 bit add; R2-R2+4 32 bit sub; R4=R3-R2 Goto Loop if R4-0 Loop: LW ADDI SW ADDI SUB BNE Z Assume that the initial value of R3 is R2 + 12. Throughout this exercise assume the simple 5 stage pipeline (IF, ID, EX, MEM, WB) discussed in class. For this problem assume that branches are resolved during the MEM stage of the pipeline. Show the timing of this instruction sequence without any forwarding hardware. Use a timing chart like: a) Cycle 2 4 LW R1, 0(R2) ADDI RI, RI, #1 IF IDEXMEM WB IF Assume that a branch is handled by stalling until the branch target is known. If all memory references are cache hits, how many cycles does this loop take to execute? b) Show the timing of this instruction sequence with normal forwarding hardware. Assume that the branch is handled by predicting it as not taken. If the branch is taken then the pipeline is flushed and the branch target is fetched once the target is known. If all memory references hit in the cache, how many cvcles does this loop take to execute? c) Assume the pipeline uses a single-cycle delayed branch and forwarding. Schedule the instructions in the loop including the branch delay slot. You may reorder instructions and modify the individual instruction operands, but do not undertake other loop transformations that change the number or opcode of the instructions in the loop. Show the pipeline timing diagram and compute the number of cycles needed to execute the entire loop R1, 0 (R2) R1, R1, #1 0 (R2), R1 R2, R2, #4 R4, R3, R2 R4, Loop R1 = MEM [R2+0] 32 bit add; R1=R1+1 MEM [R2 + 0] = RI 32 bit add; R2-R2+4 32 bit sub; R4=R3-R2 Goto Loop if R4-0 Loop: LW ADDI SW ADDI SUB BNE Z Assume that the initial value of R3 is R2 + 12. Throughout this exercise assume the simple 5 stage pipeline (IF, ID, EX, MEM, WB) discussed in class. For this problem assume that branches are resolved during the MEM stage of the pipeline. Show the timing of this instruction sequence without any forwarding hardware. Use a timing chart like: a) Cycle 2 4 LW R1, 0(R2) ADDI RI, RI, #1 IF IDEXMEM WB IF Assume that a branch is handled by stalling until the branch target is known. If all memory references are cache hits, how many cycles does this loop take to execute? b) Show the timing of this instruction sequence with normal forwarding hardware. Assume that the branch is handled by predicting it as not taken. If the branch is taken then the pipeline is flushed and the branch target is fetched once the target is known. If all memory references hit in the cache, how many cvcles does this loop take to execute? c) Assume the pipeline uses a single-cycle delayed branch and forwarding. Schedule the instructions in the loop including the branch delay slot. You may reorder instructions and modify the individual instruction operands, but do not undertake other loop transformations that change the number or opcode of the instructions in the loop. Show the pipeline timing diagram and compute the number of cycles needed to execute the entire loop