Answered step by step

Verified Expert Solution

Question

1 Approved Answer

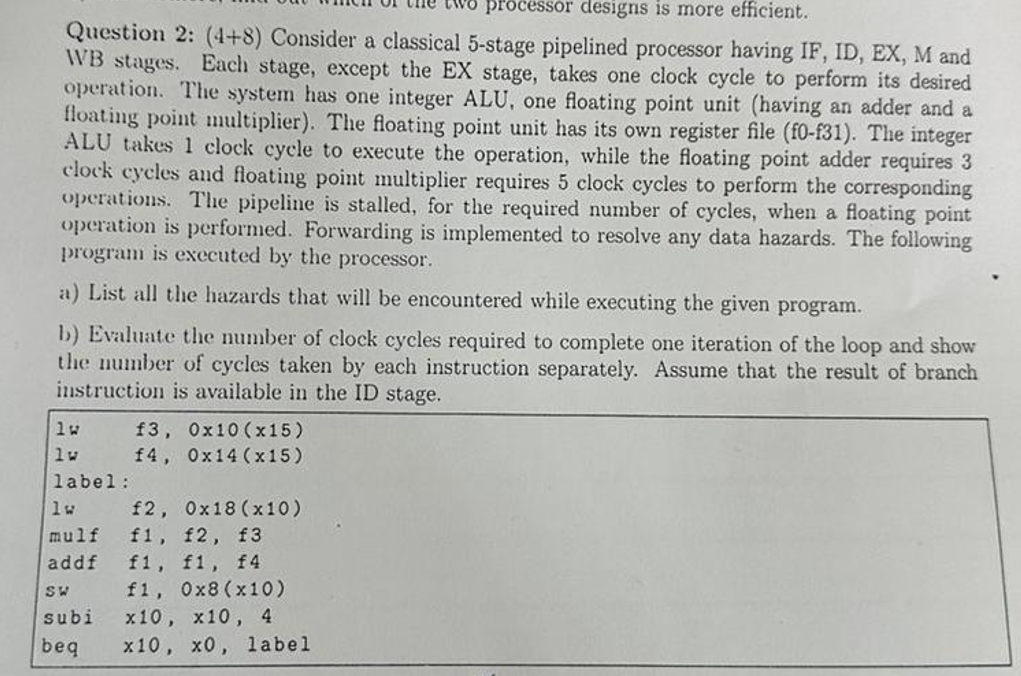

RISCV Computer Architechture Consider a classical 5 - stage pipelined processor having IF , ID , EX , M and WB stages. Each stage, except

RISCV Computer Architechture Consider a classical stage pipelined processor having IF ID EX M and

WB stages. Each stage, except the EX stage, takes one clock cycle to perform its desired

operation. The system has one integer ALU, one floating point unit having an adder and a

floating point multiplier The floating point unit has its own register file The integer

ALU takes clock cycle to execute the operation, while the floating point adder requires

clock cycles and floating point multiplier requires clock cycles to perform the corresponding

operations. The pipeline is stalled, for the required number of cycles, when a floating point

operation is performed. Forwarding is implemented to resolve any data hazards. The following

program is executed by the processor.

a List all the hazards that will be encountered while executing the given program.

b Evaluate the number of clock cycles required to complete one iteration of the loop and show

the number of cycles taken by each instruction separately. Assume that the result of branch

instruction is available in the ID stage.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started