Send me a book reference where I can found an example about memory management of a smartphone'hardware system (with smartphone brand and model)

I've attached a example (but pentium'memory management)

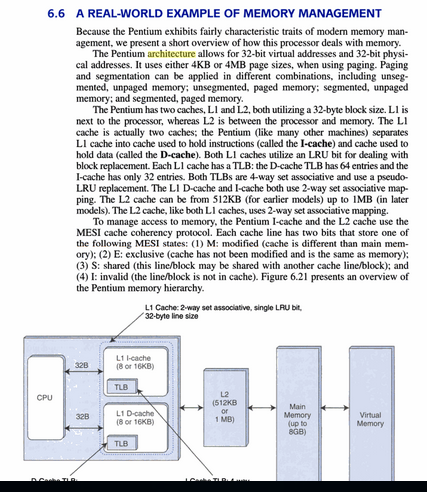

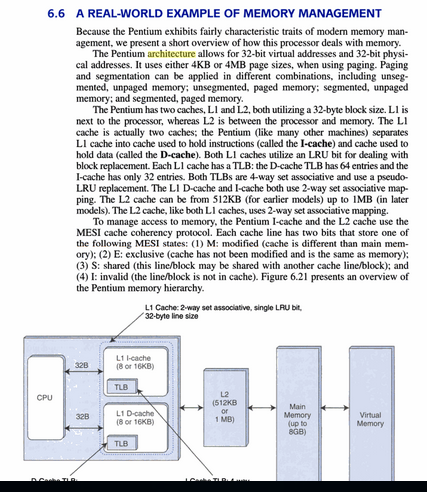

6.6 A REAL-WORLD EXAMPLE OF MEMORY MANAGEMENT Because the Pentium exhibits fairly characteristic traits of modern memory man agement, we present a short overview of how this processor deals with memory. The Pentium architecture allows for 32-bit virtual addresses and 32-bit physi cal addresses. It uses either 4KB or 4MB page sizes, when using paging. Paging and segmentation can be applied in different combinations, including unseg mented, unpaged memory; unsegmented, paged memory: segmented, unpagecd memory: and segmented, paged memory The Pentium has two caches, LI and L2, both utilizing a 32-byte block size. L1 is next to the processor, whereas L2 is between the processor and memory. The Ll cache is actually two caches; the Pentium (like many other machines) separates LI cache into cache used to hold instructions (called the I-cache) and cache used to hold data (called the D-cache). Both L1 caches utilize an LRU bit for dealing with block replacement. Each LI cache has a TLB: the D-cache TLB has 64 entries and the I-cache has only 32 entries. Both TLBs are 4-way set associative and use a pseudo- LRU replacement. The LI D-cache and I-cache both use 2-way set associative map- ping. The L2 cache can be from 512KB (for earlier models) up to IMB (in later models). The L2 cache, like both LI caches, uses 2-way set associative mapping. To manage access to memory, the Pentium I-cache and the L2 cache use the MESI cache coherency protocol. Each cache line has two bits that store one of the following MESI states: (1) M: modified (cache is different than main mem- ory): (2) E: exclusive (cache has not been modified and is the same as memory) (3) S: shared (this line/block may be shared with another cache line/block); and (4) I: invalid (the line/block is not in cache). Figure 6.21 presents an overview of the Pentium memory hierarchy. L1 Cache: 2mry set associative, single LRU bit, 32-byte line size L1 I-cache 8 or 16KB 32B TLB L2 512KB CPU Main Memory (up to G8) L1 D-cache (8 or 16KB) Virtual Memory 32B MEB) TLB 6.6 A REAL-WORLD EXAMPLE OF MEMORY MANAGEMENT Because the Pentium exhibits fairly characteristic traits of modern memory man agement, we present a short overview of how this processor deals with memory. The Pentium architecture allows for 32-bit virtual addresses and 32-bit physi cal addresses. It uses either 4KB or 4MB page sizes, when using paging. Paging and segmentation can be applied in different combinations, including unseg mented, unpaged memory; unsegmented, paged memory: segmented, unpagecd memory: and segmented, paged memory The Pentium has two caches, LI and L2, both utilizing a 32-byte block size. L1 is next to the processor, whereas L2 is between the processor and memory. The Ll cache is actually two caches; the Pentium (like many other machines) separates LI cache into cache used to hold instructions (called the I-cache) and cache used to hold data (called the D-cache). Both L1 caches utilize an LRU bit for dealing with block replacement. Each LI cache has a TLB: the D-cache TLB has 64 entries and the I-cache has only 32 entries. Both TLBs are 4-way set associative and use a pseudo- LRU replacement. The LI D-cache and I-cache both use 2-way set associative map- ping. The L2 cache can be from 512KB (for earlier models) up to IMB (in later models). The L2 cache, like both LI caches, uses 2-way set associative mapping. To manage access to memory, the Pentium I-cache and the L2 cache use the MESI cache coherency protocol. Each cache line has two bits that store one of the following MESI states: (1) M: modified (cache is different than main mem- ory): (2) E: exclusive (cache has not been modified and is the same as memory) (3) S: shared (this line/block may be shared with another cache line/block); and (4) I: invalid (the line/block is not in cache). Figure 6.21 presents an overview of the Pentium memory hierarchy. L1 Cache: 2mry set associative, single LRU bit, 32-byte line size L1 I-cache 8 or 16KB 32B TLB L2 512KB CPU Main Memory (up to G8) L1 D-cache (8 or 16KB) Virtual Memory 32B MEB) TLB