Question

Shown below is a PMOS current mirror with VDD = 1.8 V, Ibias = 150 A, R = 2 k2, and all transistors sized

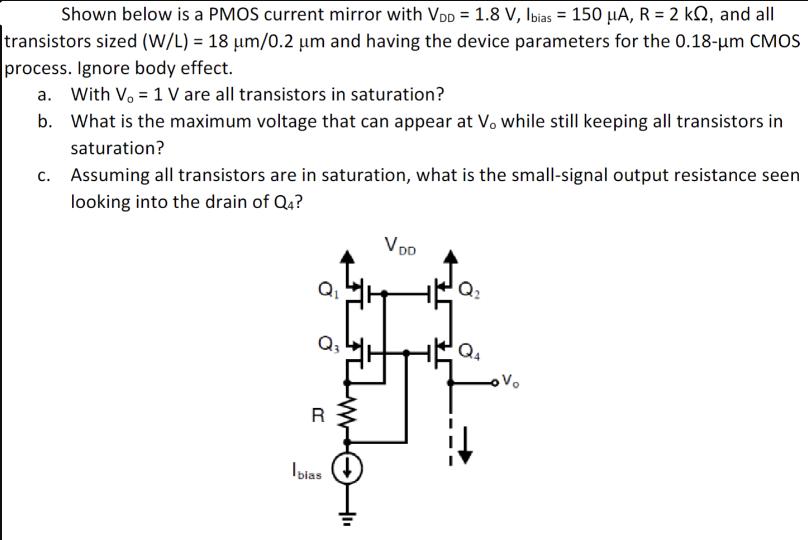

Shown below is a PMOS current mirror with VDD = 1.8 V, Ibias = 150 A, R = 2 k2, and all transistors sized (W/L) = 18 m/0.2 m and having the device parameters for the 0.18-m CMOS process. Ignore body effect. a. With V = 1 V are all transistors in saturation? b. What is the maximum voltage that can appear at V. while still keeping all transistors in saturation? c. Assuming all transistors are in saturation, what is the small-signal output resistance seen looking into the drain of Q4? R Ibias VDD Vo

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Heres the analysis of the PMOS current mirror shown a To determine if all transistors are in saturation with Vo 1 V we need to consider the condition ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Analysis and Design of Analog Integrated Circuits

Authors: Paul R. Gray, Paul J. Hurst Stephen H. Lewis, Robert G. Meyer

5th edition

1111827052, 1285401107, 9781285401102 , 978-0470245996

Students also viewed these Algorithms questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App