Answered step by step

Verified Expert Solution

Question

1 Approved Answer

(State Diagram and verilog) 2. Design a circuit that has two inputs, clk and X, and produces one output O. X may change every clock

(State Diagram and verilog)

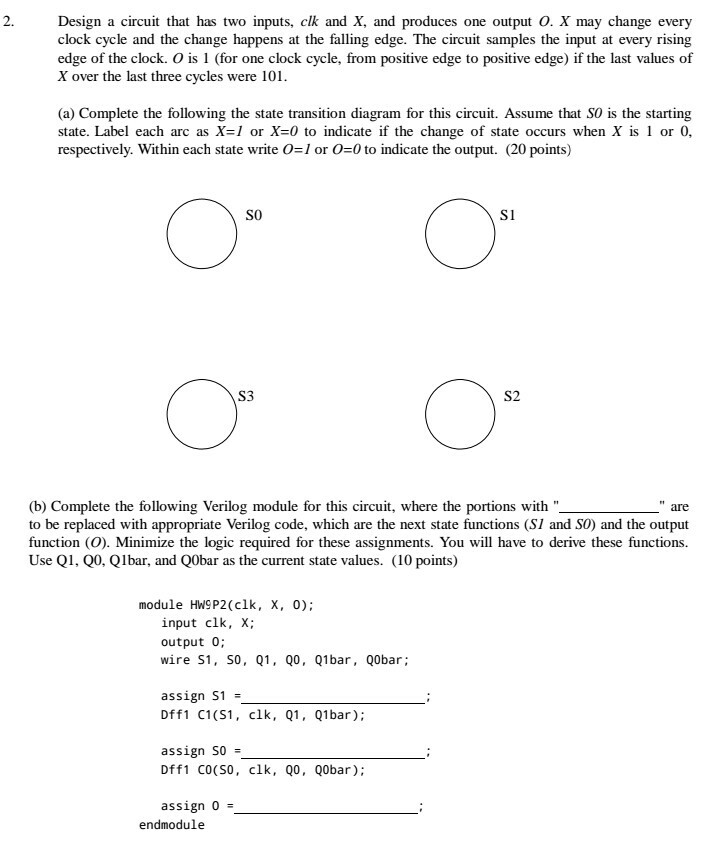

2. Design a circuit that has two inputs, clk and X, and produces one output O. X may change every clock cycle and the change happens at the falling edge. The circuit samples the input at every rising edge of the clock. O is 1 (for one clock cycle, from positive edge to positive edge) if the last values of X over the last three cycles were 101 (a) Complete the following the state transition diagram for this circuit. Assume that S0 is the starting state. Label each arc as X=1 or X=0 to indicate if the change of state occurs when X is 1 or 0, respectively. Within each state write O-1 or O 0 to indicate the output. (20 points) SO S1 S3 S2 (b) Complete the following Verilog module for this circuit, where the portions with " to be replaced with appropriate Verilog code, which are the next state functions (SI and S0) and the output function (O). Minimize the logic required for these assignments. You will have to derive these functions. Use Q1, Q0, Qlbar, and Q0bar as the current state values. (10 points) are module HW9P2 (clk, X, 0); input clk, X; output 0 wire S1, S0, Q1, 0, Q1bar, Q0bar; assign S1 Dff1 C1(S1, clk, Q1, Q1bar); assign S0 Dff1 CO(S0, clk, Q0, 00bar); assign 0 - endmodule

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started