Answered step by step

Verified Expert Solution

Question

1 Approved Answer

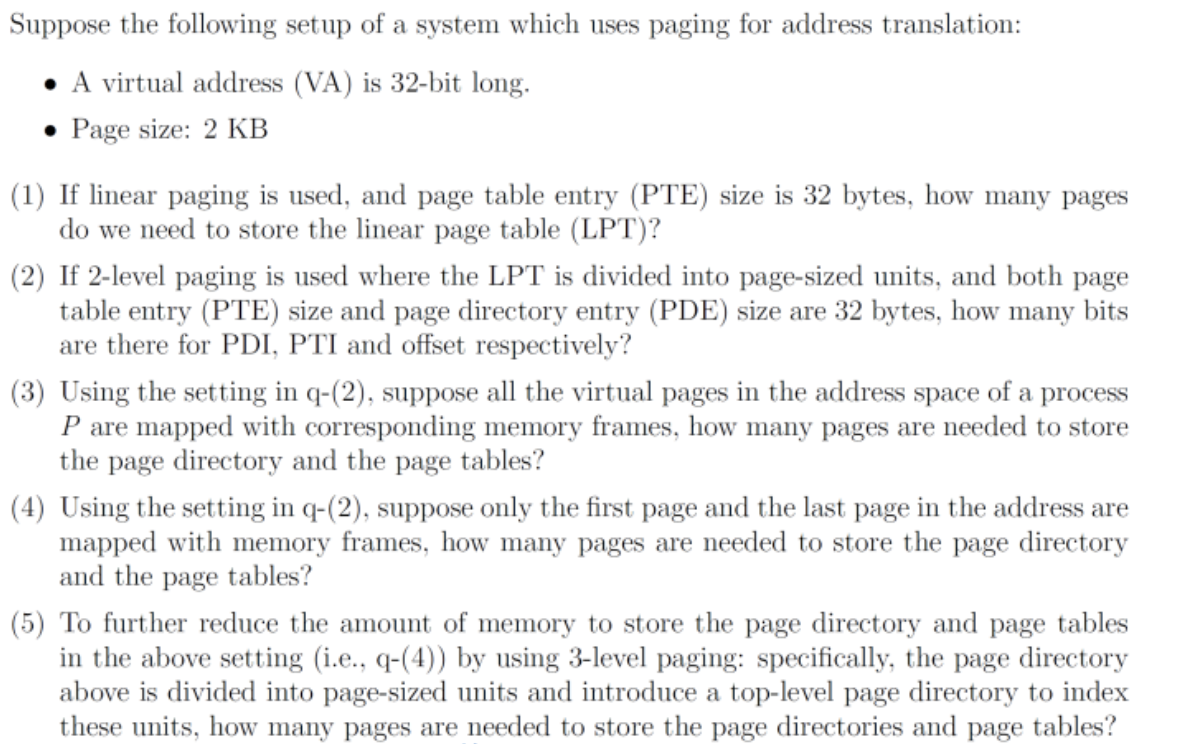

Suppose the following setup of a system which uses paging for address translation: A virtual address ( V A ) is 3 2 - bit

Suppose the following setup of a system which uses paging for address translation:

A virtual address is bit long.

Page size:

If linear paging is used, and page table entry PTE size is bytes, how many pages

do we need to store the linear page table LPT

If level paging is used where the LPT is divided into pagesized units, and both page

table entry PTE size and page directory entry PDE size are bytes, how many bits

are there for PDI, PTI and offset respectively?

Using the setting in suppose all the virtual pages in the address space of a process

are mapped with corresponding memory frames, how many pages are needed to store

the page directory and the page tables?

Using the setting in q suppose only the first page and the last page in the address are

mapped with memory frames, how many pages are needed to store the page directory

and the page tables?

To further reduce the amount of memory to store the page directory and page tables

in the above setting ie q by using level paging: specifically, the page directory

above is divided into pagesized units and introduce a toplevel page directory to index

these units, how many pages are needed to store the page directories and page tables?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started