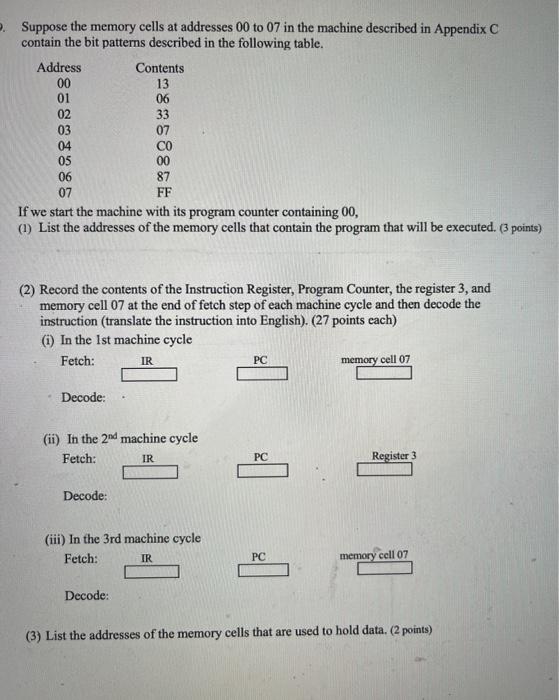

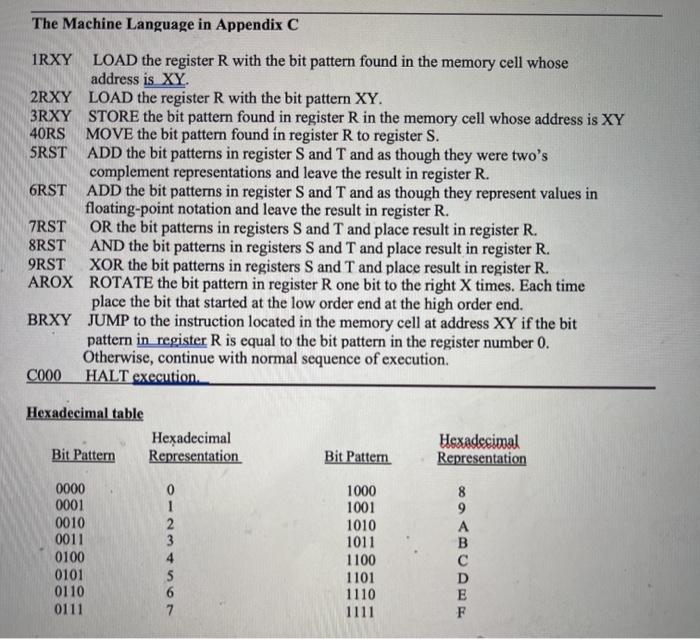

Suppose the memory cells at addresses 00 to 07 in the machine described in Appendix contain the bit patterns described in the following table. Address Contents 00 13 01 06 02 33 03 07 04 05 00 06 87 07 FF If we start the machine with its program counter containing 00, (1) List the addresses of the memory cells that contain the program that will be executed. (3 points) (2) Record the contents of the Instruction Register, Program Counter, the register 3, and memory cell 07 at the end of fetch step of each machine cycle and then decode the instruction (translate the instruction into English). (27 points each) (1) In the 1st machine cycle Fetch: memory cell 07 IR PC Decode: (ii) In the 2nd machine cycle Fetch: IR PC Register 3 Decode: (iii) In the 3rd machine cycle Fetch: IR PC memory cell 07 Decode: (3) List the addresses of the memory cells that are used to hold data. (2 points) The Machine Language in Appendix C 1RXY LOAD the register R with the bit pattern found in the memory cell whose address is XY 2RXY LOAD the register R with the bit pattern XY. 3RXY STORE the bit pattern found in register R in the memory cell whose address is XY 40RS MOVE the bit pattern found in register R to register S. SRST ADD the bit patterns in register S and T and as though they were two's complement representations and leave the result in register R. 6RST ADD the bit patterns in register S and T and as though they represent values in floating-point notation and leave the result in register R. 7RST OR the bit patterns in registers S and T and place result in register R. SRST AND the bit patterns in registers S and T and place result in register R. ORST XOR the bit patterns in registers S and T and place result in register R. AROX ROTATE the bit pattern in register R one bit to the right X times. Each time place the bit that started at the low order end at the high order end. BRXY JUMP to the instruction located in the memory cell at address XY if the bit pattern in register R is equal to the bit pattern in the register number 0. Otherwise, continue with normal sequence of execution. C000 HALT execution Hexadecimal table Hexadecimal Bit Pattern Representation Hexadecimal Representation Bit Pattern 0000 0001 0010 0011 0100 0101 0110 0111 0 1 2 3 4 5 6 7 1000 1001 1010 1011 1100 1101 1110 1111 8 9 B E F