Question

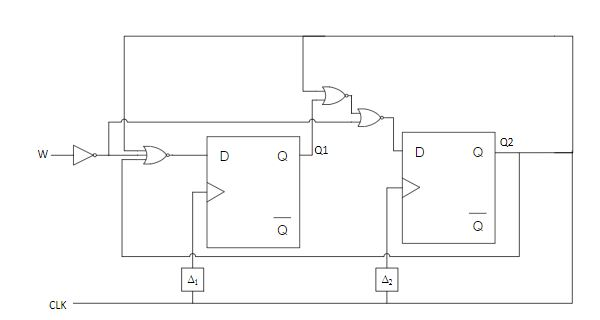

The following circuit could be used to implement the vehicle speed problem from class. Now we wish to analyze its timing properties. Suppose that each

The following circuit could be used to implement the vehicle speed problem from class. Now we wish to analyze its timing properties. Suppose that each flip flop has a setup time of 4 ns, hold time of 3.5 ns, and experiences delay in the range of 12 ns. The 3-input NOR gate has a delay of 3 ns. The other 2-input NOR gates have delays of 2 ns each.The inverter has a delay of 1 ns.

a) First assume no clock skew occurs. What is the maximum frequency that the circuit can be run at?

Show all relevant work.

b) Suppose ?1= 0 ns, ?2= 2 ns. What is the new value of the maximum frequency? Will there be any

hold time violations? Show all relevant work.

c) If there are hold time violations in part (b), propose a solution. The analog designers insist that the skew cannot be changed. If there are no hold time violations in part (b), how much margin (in nanoseconds) exists over a hold time violation occurring?

02 01 CLK 02 01 CLK

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started