Question

The following code segment is to be executed on a RISC processor with: 1: R1 R2 + R3 2: R4 R1 + R2 3:

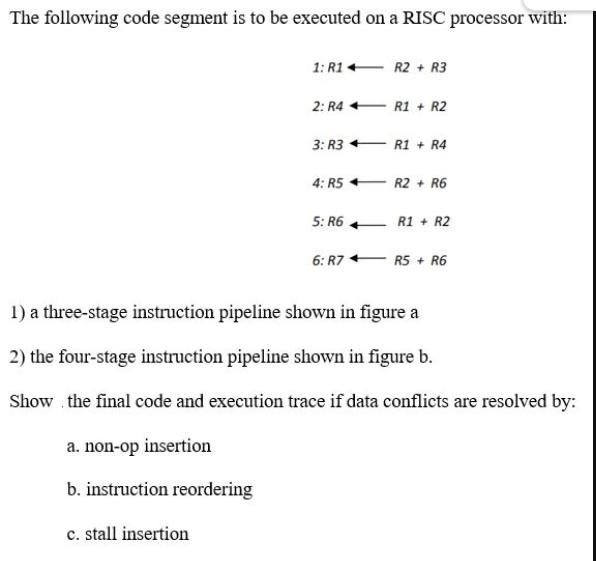

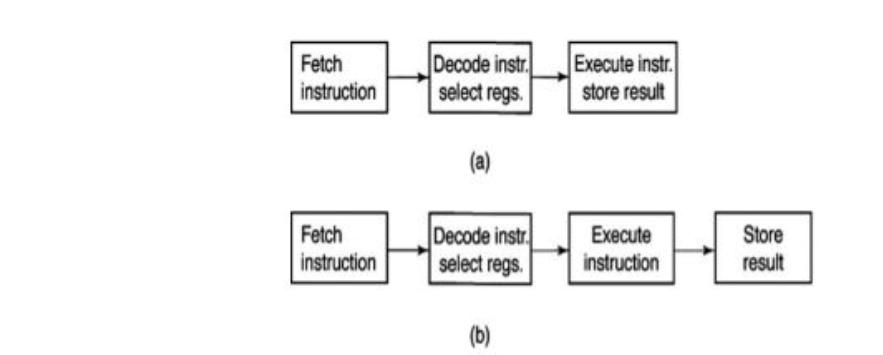

The following code segment is to be executed on a RISC processor with: 1: R1 R2 + R3 2: R4 R1 + R2 3: R3+ R1 + R4 4: R5 -R2R6 5: R6 R1 + R2 6: R7 R5+ R6 1) a three-stage instruction pipeline shown in figure a 2) the four-stage instruction pipeline shown in figure b. Show the final code and execution trace if data conflicts are resolved by: a. non-op insertion b. instruction reordering c. stall insertion Fetch instruction Decode instr select regs. Execute instr. store result (a) Fetch Decode instr Execute Store instruction select regs. instruction result (b)

Step by Step Solution

There are 3 Steps involved in it

Step: 1

To handle data conflicts in a pipeline there are several techniques that can be used such as nonoperation NOP insertion instruction reordering and sta...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Computer organization and architecture designing for performance

Authors: william stallings

8th edition

136073735, 978-0136073734

Students also viewed these Computer Network questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App