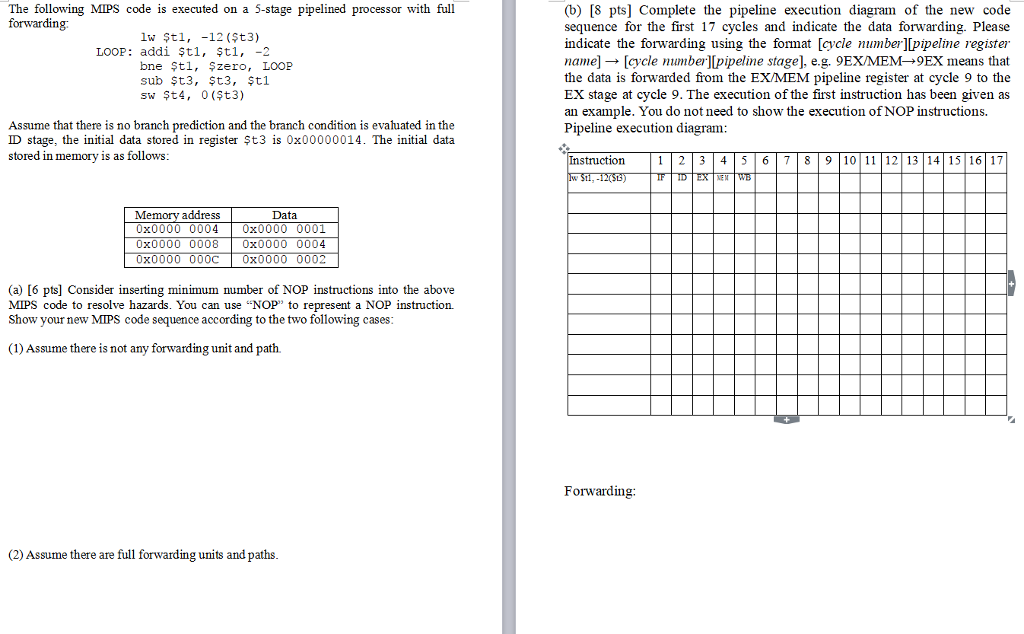

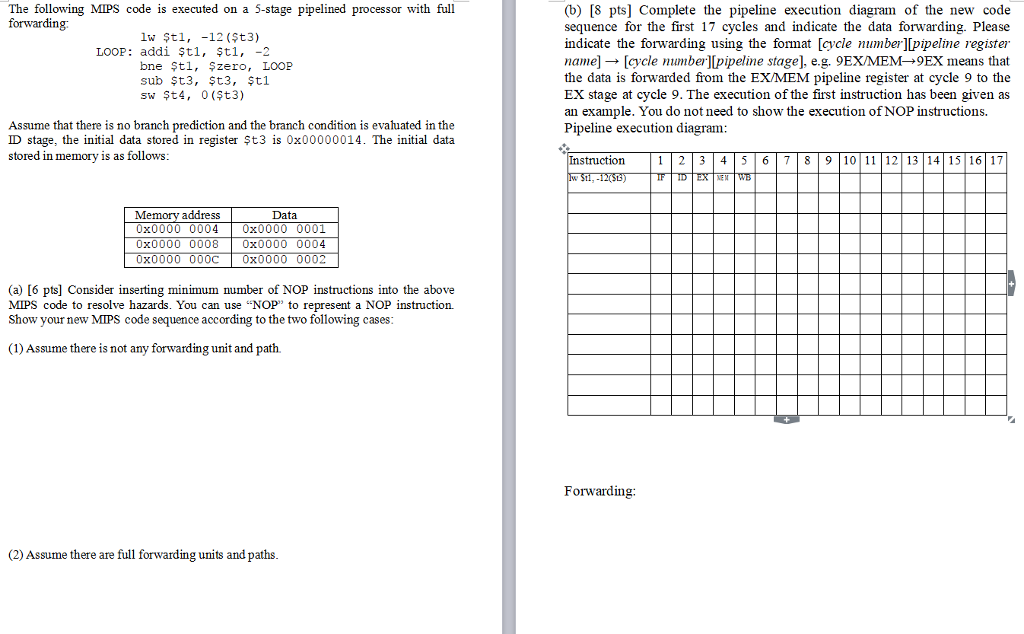

The following MIPS code is executed on a 5-s forwarding stage pipelined processor with full (b) [8 pts] Complete the pipeline execution diagram of the new code sequence for the first 17 cycles and indicate the data forwarding. Please indicate the forwarding using the format [cycle number][pipeline register name] [cycle number][Pipeline stage], e.g. 9EXMEM9EX means that the data is forwarded from the EXMEM pipeline register at cycle 9 to the EX stage at cycle 9. The execution of the first instruction has been given as an example. You do not need to show the execution of NOP instructions. Pipeline execution diagram lw tl, -12 ($t3) LOOP: addi $t1, $tl, 2 bne $tl, zero, LOOP sub $t3, $t3, $t1 Assume that there is no branch prediction and the branch condition is evahuated in the ID stage, the initial data stored in register $t3 is 0x00000014. The initial data stored in memory is as follows struction 12 34 5 6 78 9 10 11 12 13 14 15 16 17 Me address Data x0000 0x0000 0004 Ox0000 0008 (a) [6 pts] Consider inserting minimum number of NOP instructions into the above MIPS code to resolve hazards, You can use "NOP to represent a NOP instruction Show your new MIPS code sequence according to the two following cases (1) Assume there is not any forwarding unit and path. Forwarding: (2) Assume there are full forwarding units and paths The following MIPS code is executed on a 5-s forwarding stage pipelined processor with full (b) [8 pts] Complete the pipeline execution diagram of the new code sequence for the first 17 cycles and indicate the data forwarding. Please indicate the forwarding using the format [cycle number][pipeline register name] [cycle number][Pipeline stage], e.g. 9EXMEM9EX means that the data is forwarded from the EXMEM pipeline register at cycle 9 to the EX stage at cycle 9. The execution of the first instruction has been given as an example. You do not need to show the execution of NOP instructions. Pipeline execution diagram lw tl, -12 ($t3) LOOP: addi $t1, $tl, 2 bne $tl, zero, LOOP sub $t3, $t3, $t1 Assume that there is no branch prediction and the branch condition is evahuated in the ID stage, the initial data stored in register $t3 is 0x00000014. The initial data stored in memory is as follows struction 12 34 5 6 78 9 10 11 12 13 14 15 16 17 Me address Data x0000 0x0000 0004 Ox0000 0008 (a) [6 pts] Consider inserting minimum number of NOP instructions into the above MIPS code to resolve hazards, You can use "NOP to represent a NOP instruction Show your new MIPS code sequence according to the two following cases (1) Assume there is not any forwarding unit and path. Forwarding: (2) Assume there are full forwarding units and paths