Answered step by step

Verified Expert Solution

Question

1 Approved Answer

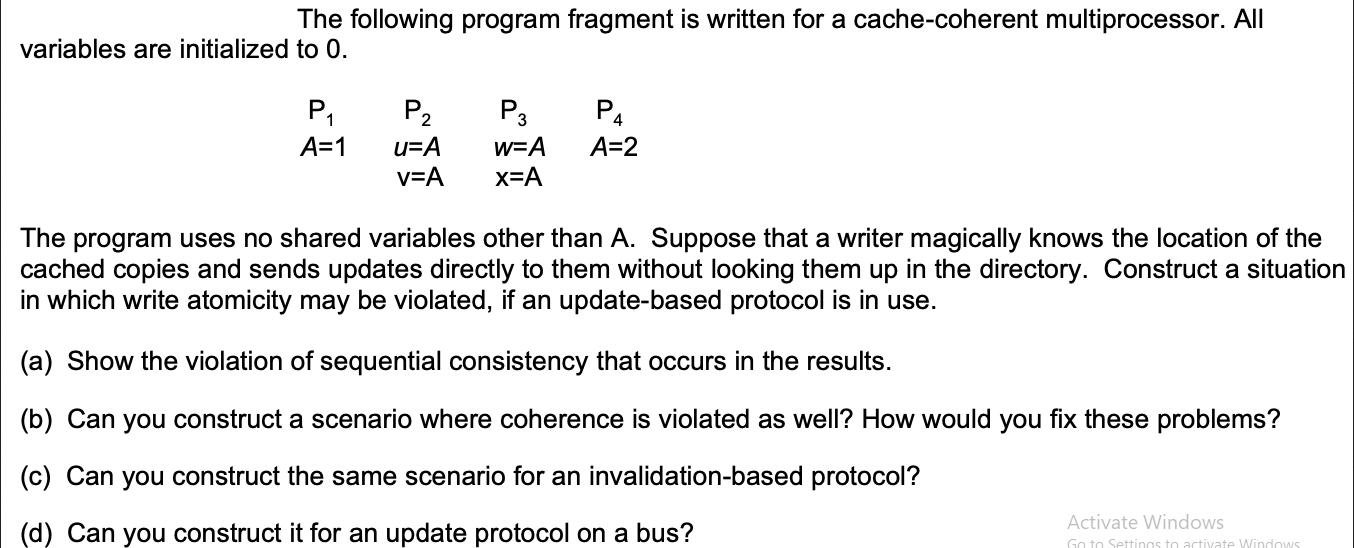

The following program fragment is written for a cache-coherent multiprocessor. All variables are initialized to 0. P A=1 P u=A v=A P3 W=A x=A

The following program fragment is written for a cache-coherent multiprocessor. All variables are initialized to 0. P A=1 P u=A v=A P3 W=A x=A P A=2 The program uses no shared variables other than A. Suppose that a writer magically knows the location of the cached copies and sends updates directly to them without looking them up in the directory. Construct a situation in which write atomicity may be violated, if an update-based protocol is in use. (a) Show the violation of sequential consistency that occurs in the results. (b) Can you construct a scenario where coherence is violated as well? How would you fix these problems? (c) Can you construct the same scenario for an invalidation-based protocol? (d) Can you construct it for an update protocol on a bus? Activate Windows Go to Settings to activate Windows

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started