Question

The following structural Verilog module is for a 3- bit counter. The outputs of the counter are C2 (most significant), C1, and C0 (least significant).

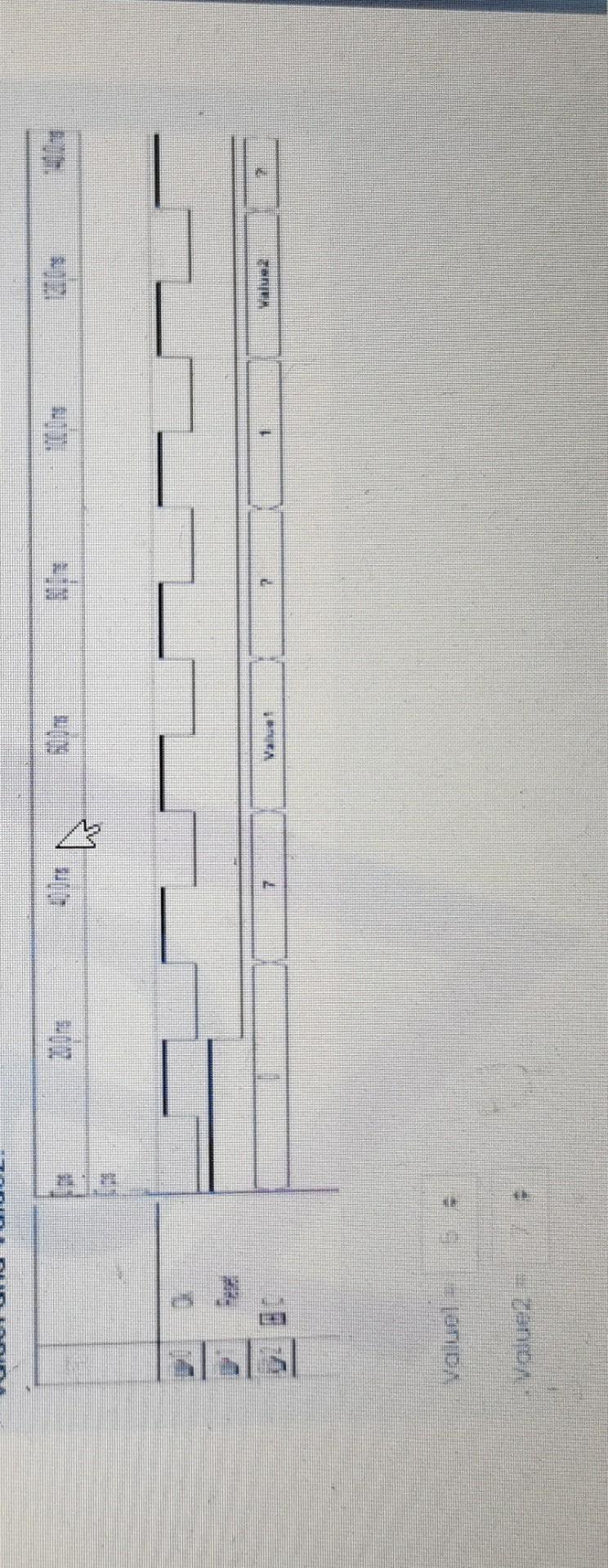

The following structural Verilog module is for a 3- bit counter. The outputs of the counter are C2 (most significant), C1, and C0 (least significant). The module contains three gates: Two inverters and 2-input XOR gate. The module definitions of the gates are given as comments in the code. The module also contains three D-type flip-flops (FF). The module definitions of the FF is given as a comment in the code. module counter3_v1 (Reset, CIk, C2, C1, C0) ; input Reset, clk; output C2,C1,C0; //Invgate (out, in) //Xorgate (out, in1, in2) Invgate (D1,C1); Xorgate (w2,C1,C2); Invgate (D2,w2); //dff1 (D, Reset, Clk, 0) dff1(1,Reset, Clk,C0); dff1(D1, Reset, Clk,C1); dff1 (D2,Reset,Clk,C2); endmodule The following waveform is generated using functional simulation for the 3-bit counter above. Notice that outputs C2, CI, and C0 are grouped together and named "C' and formatted as Unsigned Decimal*. "C2* is most significant and *CO' is least significant. Accordingly determine valuel and Value2?

arcmol= 24in2=Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started