Question

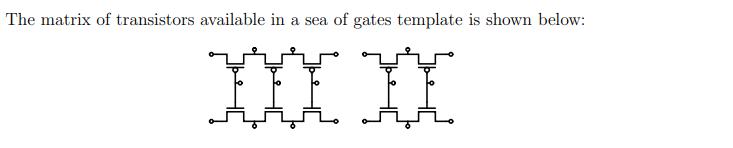

The matrix of transistors available in a sea of gates template is shown below: IIIII All n channel transistor in the template have the

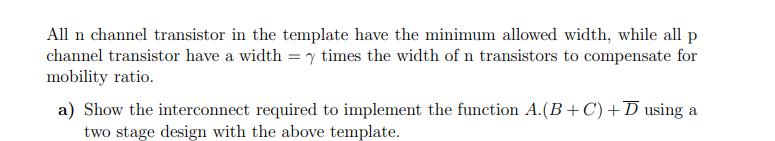

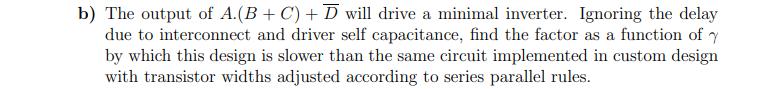

The matrix of transistors available in a sea of gates template is shown below: IIIII All n channel transistor in the template have the minimum allowed width, while all p channel transistor have a width = times the width of n transistors to compensate for mobility ratio. a) Show the interconnect required to implement the function A.(B+C) +D using a two stage design with the above template. b) The output of A.(B+C) +D will drive a minimal inverter. Ignoring the delay due to interconnect and driver self capacitance, find the factor as a function of by which this design is slower than the same circuit implemented in custom design with transistor widths adjusted according to series parallel rules.

Step by Step Solution

3.52 Rating (162 Votes )

There are 3 Steps involved in it

Step: 1

The detailed ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Analysis and Design of Analog Integrated Circuits

Authors: Paul R. Gray, Paul J. Hurst Stephen H. Lewis, Robert G. Meyer

5th edition

1111827052, 1285401107, 9781285401102 , 978-0470245996

Students also viewed these Electrical Engineering questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App