Answered step by step

Verified Expert Solution

Question

1 Approved Answer

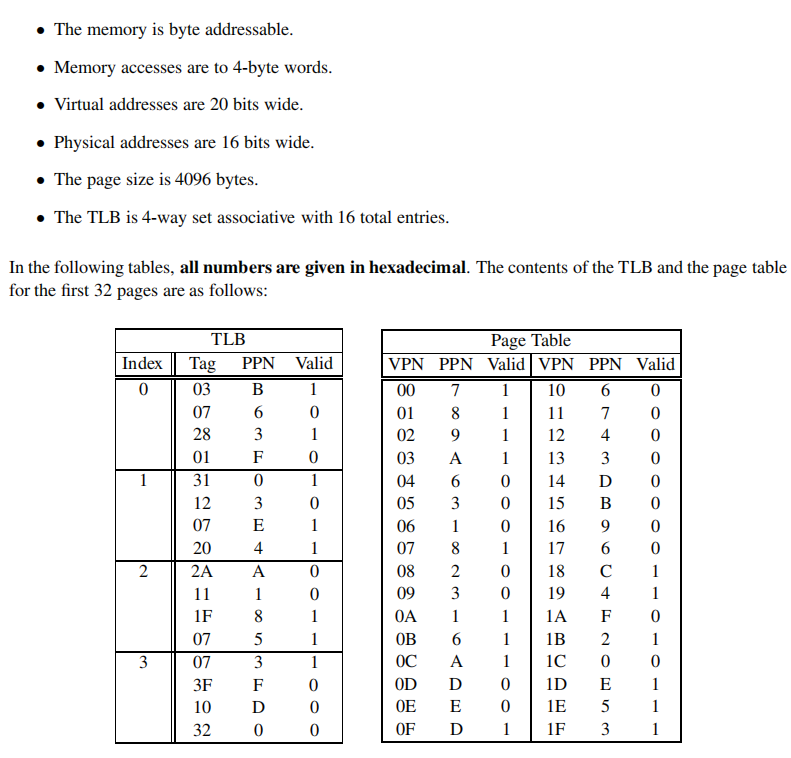

The memory is byte addressable. Memory accesses are to 4-byte words. Virtual addresses are 20 bits wide. Physical addresses are 16 bits wide. The

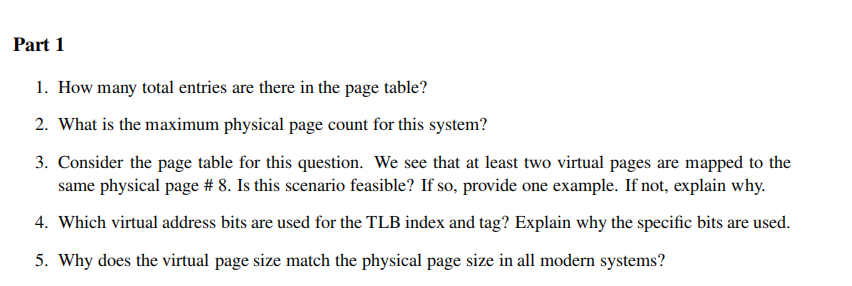

The memory is byte addressable. Memory accesses are to 4-byte words. Virtual addresses are 20 bits wide. Physical addresses are 16 bits wide. The page size is 4096 bytes. The TLB is 4-way set associative with 16 total entries. In the following tables, all numbers are given in hexadecimal. The contents of the TLB and the page table for the first 32 pages are as follows: TLB Page Table Index Tag PPN Valid VPN PPN Valid VPN PPN Valid 0 03 B 1 00 7 1 10 6 0 07 6 0 01 8 1 11 7 0 28 3 1 02 9 1 12 4 0 01 F 0 03 A 1 13 3 0 1 31 0 1 04 6 0 14 0 12 3 0 05 3 0 15 B 0 07 E 1 06 1 0 16 9 0 20 4 1 07 8 1 17 6 0 2 2A A 0 08 2 0 18 C 1 11 1 0 09 3 0 19 4 1 1F 8 1 OA 1 1 1A F 0 07 5 1 OB 6 1 1B 2 1 3 07 3 1 OC A 1 1C 0 0 3F F 0 OD 0 1D E 1 10 0 OE E 0 1E 5 1 32 0 0 OF D 1 1F 3 1 Part 1 1. How many total entries are there in the page table? 2. What is the maximum physical page count for this system? 3. Consider the page table for this question. We see that at least two virtual pages are mapped to the same physical page # 8. Is this scenario feasible? If so, provide one example. If not, explain why. 4. Which virtual address bits are used for the TLB index and tag? Explain why the specific bits are used. 5. Why does the virtual page size match the physical page size in all modern systems?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started