Answered step by step

Verified Expert Solution

Question

1 Approved Answer

The miss rate from the table is 0.0036 You have been asked to investigate the relative performance of a banked versus pipelined level 1 data

The miss rate from the table is 0.0036

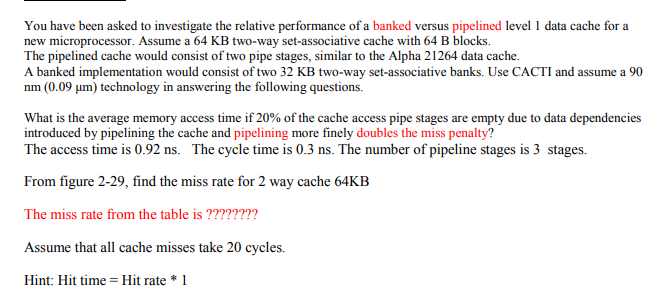

You have been asked to investigate the relative performance of a banked versus pipelined level 1 data cache for a new microprocessor. Assume a 64 KB two-way set-associative cache with 64 B blocks. The pipelined cache would consist of two pipe stages, similar to the Alpha 21264 data cache. A banked implementation would consist of two 32 KB two-way set-associative banks. Use CACTI and assume a 90 nm (0.09 um) technology in answering the following questions What is the average memory access time if 20% of the cache access pipe stages are empty due to data dependencies introduced by pipelining the cache and pipelining more finely doubles the miss penalty? The access time is 0.92 ns. The cycle time is 0.3 ns. The number of pipeline stages is 3 stages. From figure 2-29, find the miss rate for 2 way cache 64KB The miss rate from the table is ???????? Assume that all cache misses take 20 cycles. Hint: Hit time Hit rate * 1 You have been asked to investigate the relative performance of a banked versus pipelined level 1 data cache for a new microprocessor. Assume a 64 KB two-way set-associative cache with 64 B blocks. The pipelined cache would consist of two pipe stages, similar to the Alpha 21264 data cache. A banked implementation would consist of two 32 KB two-way set-associative banks. Use CACTI and assume a 90 nm (0.09 um) technology in answering the following questions What is the average memory access time if 20% of the cache access pipe stages are empty due to data dependencies introduced by pipelining the cache and pipelining more finely doubles the miss penalty? The access time is 0.92 ns. The cycle time is 0.3 ns. The number of pipeline stages is 3 stages. From figure 2-29, find the miss rate for 2 way cache 64KB The miss rate from the table is ???????? Assume that all cache misses take 20 cycles. Hint: Hit time Hit rate * 1Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started