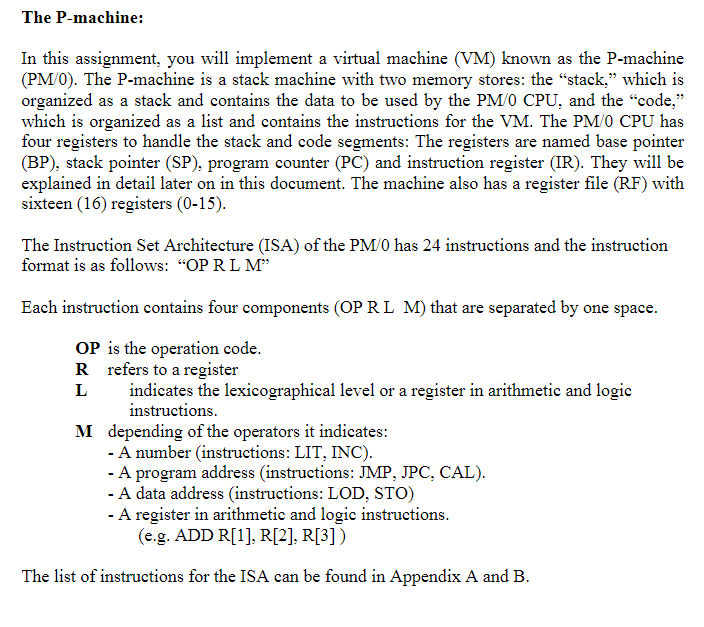

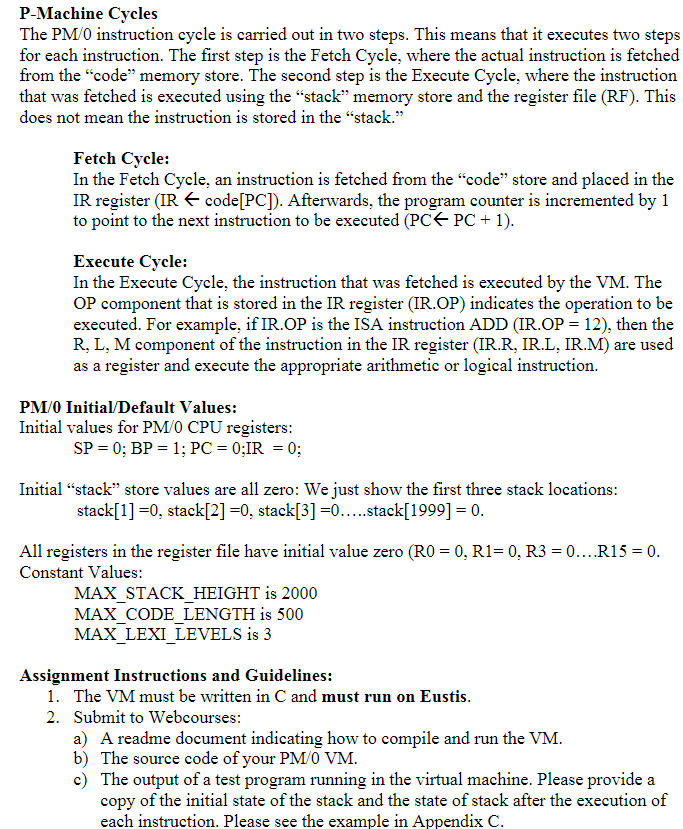

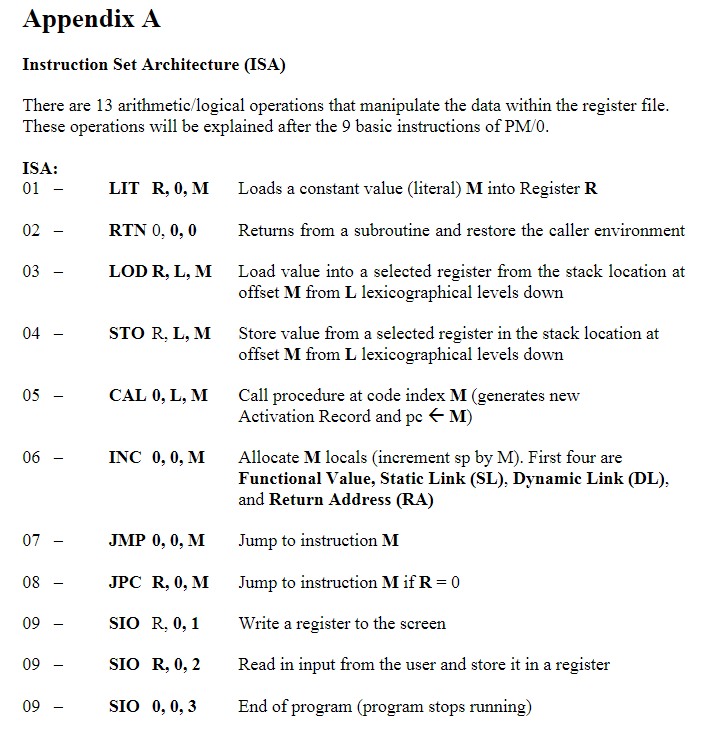

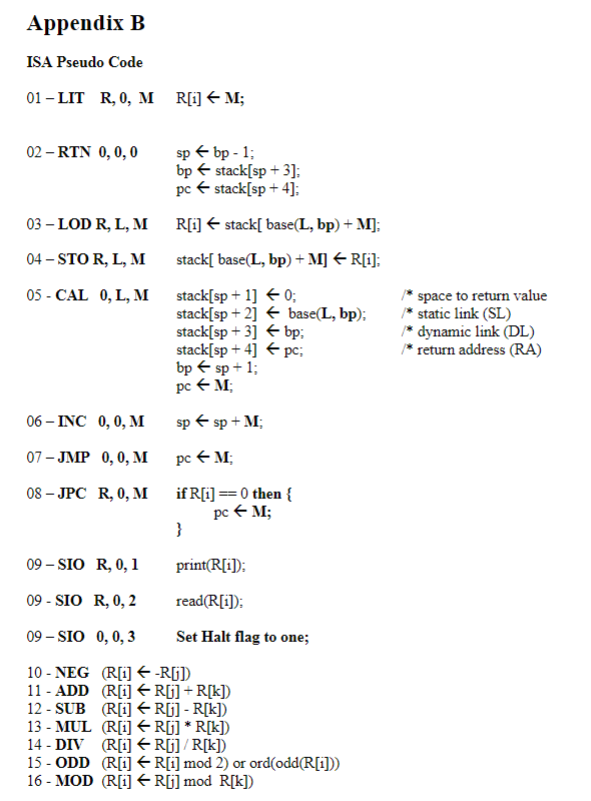

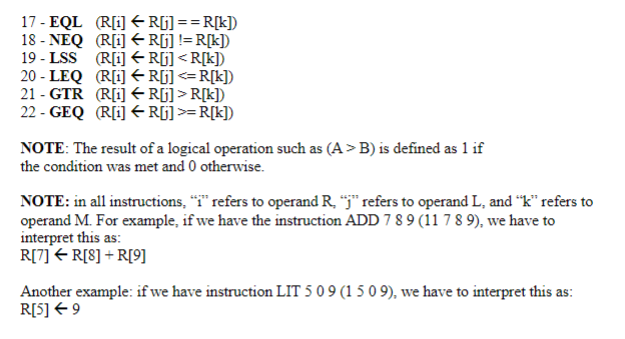

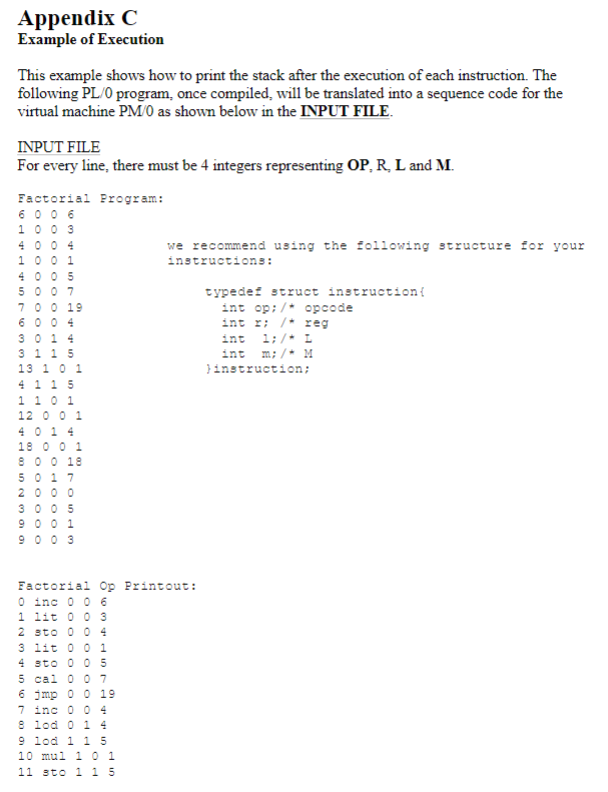

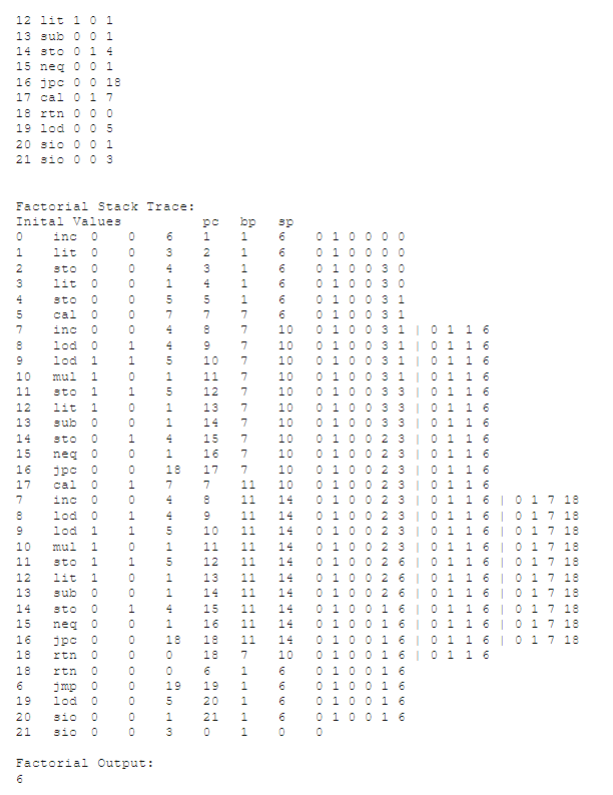

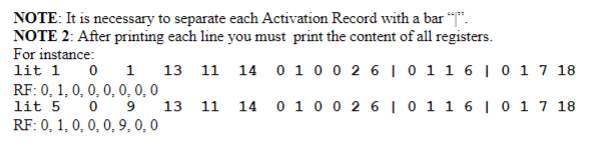

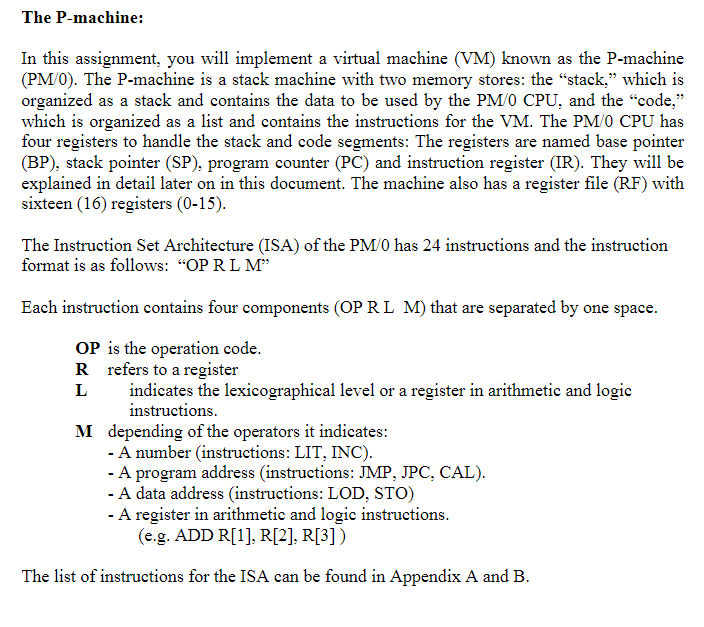

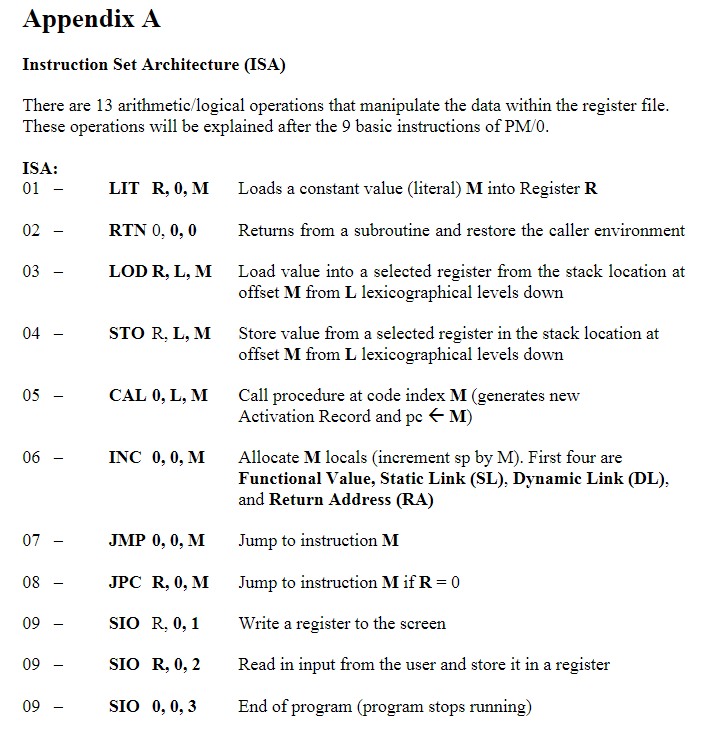

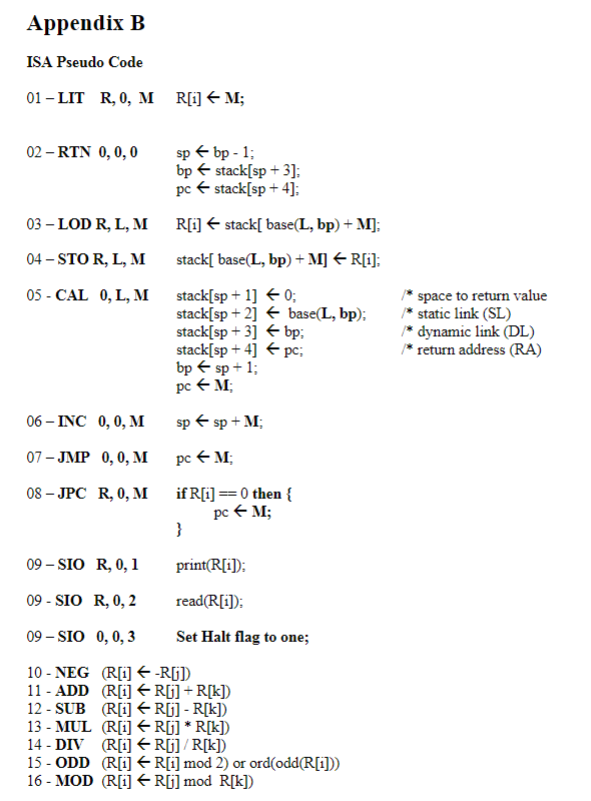

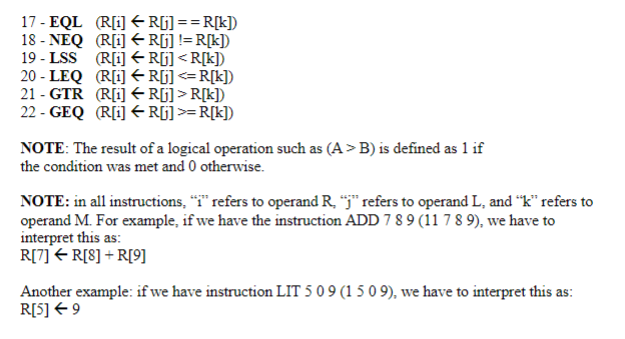

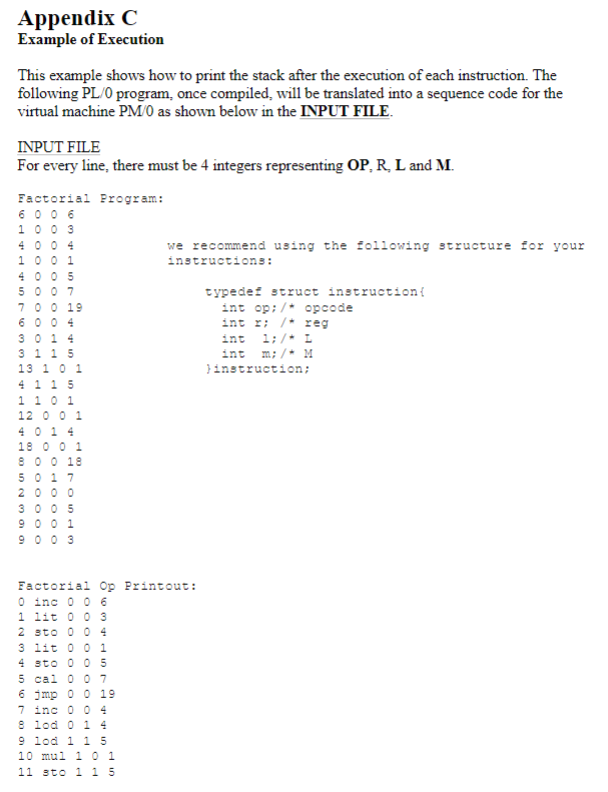

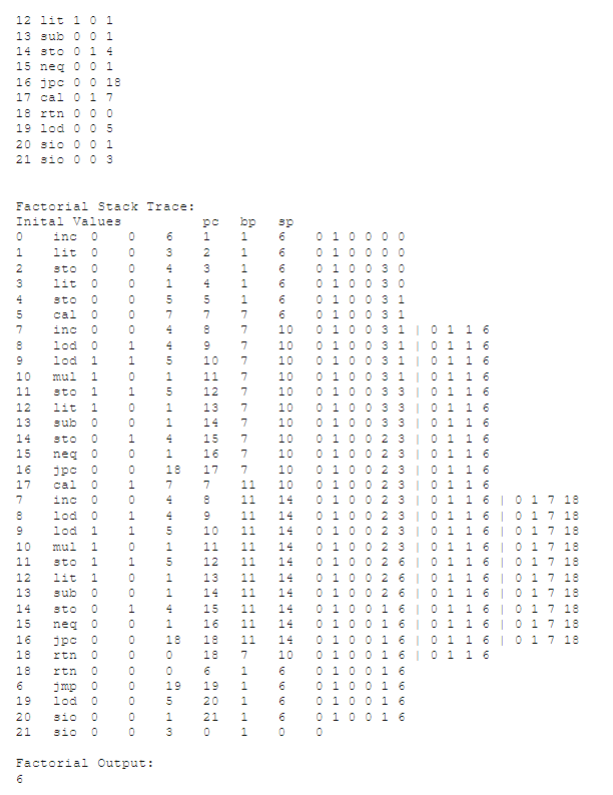

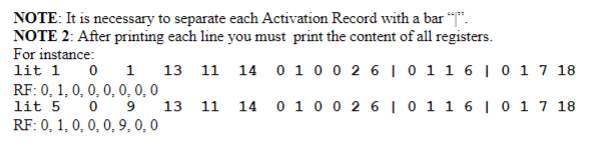

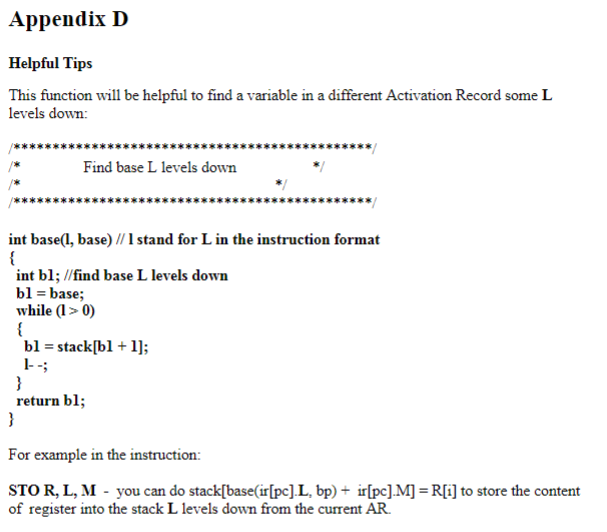

The P-machine: In this assignment, you will implement a virtual machine (VM) known as the P-machine (PM/0). The P-machine is a stack machine with two memory stores: the "stack," which is organized as a stack and contains the data to be used by the PM0 CPU, and the "code," which is organized as a list and contains the instructions for the VM. The PM/0 CPU has four registers to handle the stack and code segments: The registers are named base pointer (BP), stack pointer (SP), program counter (PC) and instruction register (IR). They will be explained in detail later on in this document. The machine also has a register file (RF) with sixteen (16) registers (0-15) The Instruction Set Architecture (ISA) of the PM/0 has 24 instructions and the instruction format is as follows: "OP R L M Each instruction contains four components (OPRL M) that are separated by one space OP is the operation code R refers to a register Lindicates the lexicographical level or a register in arithmetic and logic nstructions M depending of the operators it indicates - A number (instructions: LIT, INC) A program address (instructions: JMP, JPC, CAL) - A data address (instructions: LOD, STO) - A register in arithmetic and logic instructions e.g. ADD R[1], R[2], R[3]) The list of instructions for the ISA can be found in Appendix A and B The P-machine: In this assignment, you will implement a virtual machine (VM) known as the P-machine (PM/0). The P-machine is a stack machine with two memory stores: the "stack," which is organized as a stack and contains the data to be used by the PM0 CPU, and the "code," which is organized as a list and contains the instructions for the VM. The PM/0 CPU has four registers to handle the stack and code segments: The registers are named base pointer (BP), stack pointer (SP), program counter (PC) and instruction register (IR). They will be explained in detail later on in this document. The machine also has a register file (RF) with sixteen (16) registers (0-15) The Instruction Set Architecture (ISA) of the PM/0 has 24 instructions and the instruction format is as follows: "OP R L M Each instruction contains four components (OPRL M) that are separated by one space OP is the operation code R refers to a register Lindicates the lexicographical level or a register in arithmetic and logic nstructions M depending of the operators it indicates - A number (instructions: LIT, INC) A program address (instructions: JMP, JPC, CAL) - A data address (instructions: LOD, STO) - A register in arithmetic and logic instructions e.g. ADD R[1], R[2], R[3]) The list of instructions for the ISA can be found in Appendix A and B