Answered step by step

Verified Expert Solution

Question

1 Approved Answer

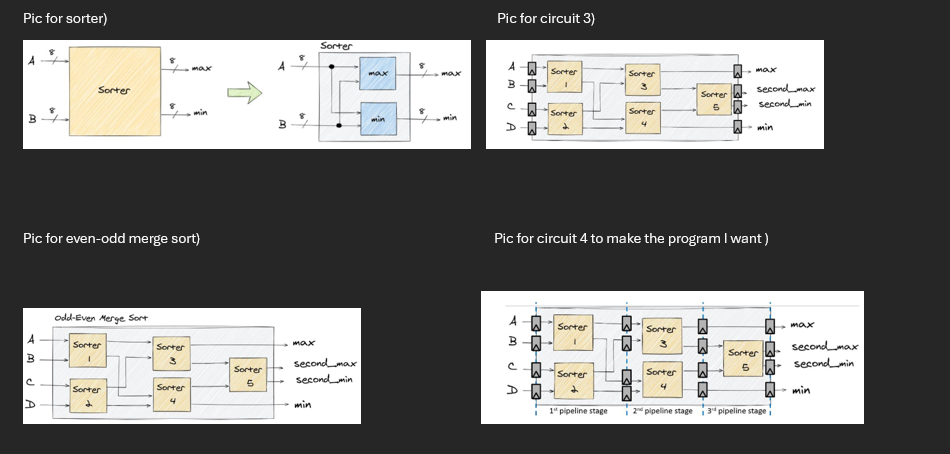

the program for the sorter i s : module sorter ( Pic for sorter ) Pic for circuit 3 ) Pic for even - odd

the program for the sorter : module sorter Pic for sorter

Pic for circuit

Pic for evenodd merge sort

Pic for circuit to make the program I want

input logic : A

input logic : B

output logic : max,

output logic : min

;

alwayscomb begin

if A B begin

max A;

min B;

end else begin

max B;

min A;

end

end

endmodule

the program for oddeven merge sort :

module evenoddmergesorter

input logic : A

input logic : B

input logic : C

input logic : D

output logic : max,

output logic : secondmax,

output logic : secondmin,

output logic : min

;

logic : sortermax;

logic : sortermin;

logic : sortermax;

logic : sortermin;

logic : sortermin;

logic : sortermax;

sorter sorterA B sortermax, sortermin;

sorter sorterC D sortermax, sortermin;

sorter sortersortermax, sortermax, max, sortermin;

sorter sortersortermin, sortermin, sortermax, min;

sorter sortersortermin, sortermax, secondmax, secondmin;

endmodule

the program for the circuit : module evenoddmergesorterwrapper

input logic clk

input logic rst

input logic : A

input logic : B

input logic : C

input logic : D

output logic : max,

output logic : secondmax,

output logic : secondmin,

output logic : min

;

logic : regA, regB, regC, regD;

logic : regmax, regsecondmax, regsecondmin, regmin;

logic : sortermax;

logic : sortermin;

logic : sortermax;

logic : sortermin;

logic : sortermin;

logic : sortermax;

Register Input

alwaysff@posedge clk begin

if rst begin

regA b;

regB b;

regC b;

regD b;

end else begin

regA A;

regB B;

regC C;

regD D;

end

end

intsantiate evenoddmergesorter circuit

evenoddmergesorter sorterregA regB, regC, regD, regmax, regsecondmax, regsecondmin, regmin;

Register Output

alwaysff@posedge clk begin

if rst begin

max b;

secondmax b;

secondmin b;

min b;

end else begin

max regmax;

secondmax regsecondmax;

secondmin regsecondmin;

min regmin;

end

end

endmodule

the program for techbench :

according all above programs i want a program for the circuit for vivado. thank you very much module evenoddmergesortertb;

parameter MEMSIZE ;

logic clk rst;

logic : A;

logic : B;

logic : C;

logic : D;

logic : max;

logic : secondmax;

logic : secondmin;

logic : min;

logic : testmemory:MEMSIZE;

integer i;

always begin

clk ;

#ns;

clk ;

#ns;

end

evenoddmergesorterwrapper sorterclk rst A B C D max, secondmax, secondmin, min;

initial begin

$monitor$time, maxh secondmaxh secondminh minh max, secondmax, secondmin, min;

$displayLoading test vectors";

$readmemhtesttv testmemory;

rst ;

repeat @posedge clk;

rst ;

for i; i

so according to all above programs i want a program for the circuit for vivado. thank you very much

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started