Answered step by step

Verified Expert Solution

Question

1 Approved Answer

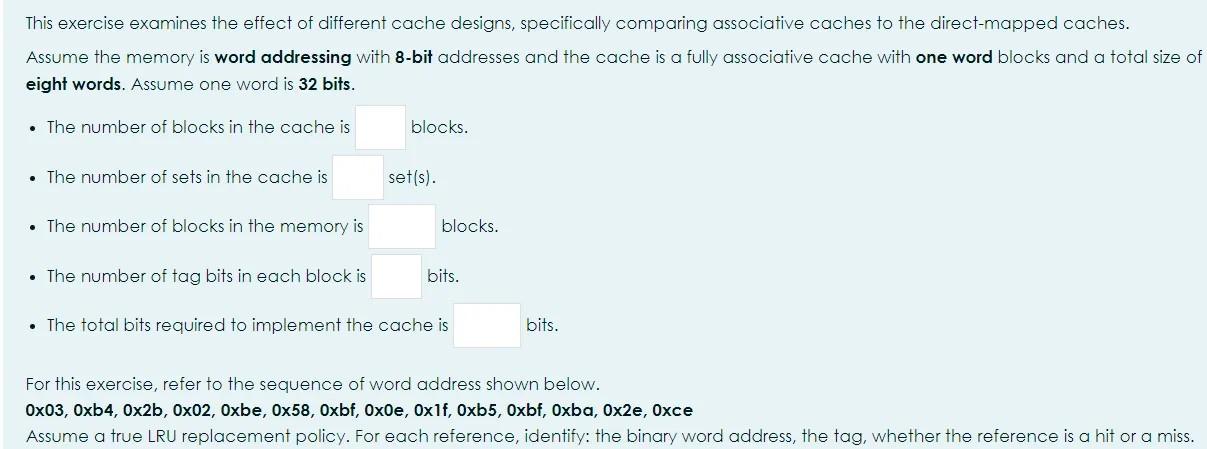

This exercise examines the effect of different cache designs, specifically comparing associative caches to the direct-mapped caches. Assume the memory is word addressing with 8-bit

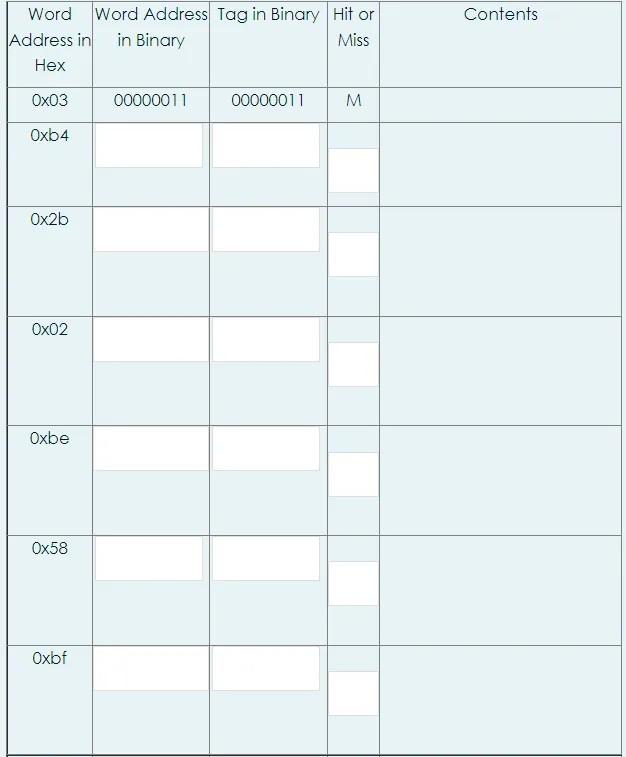

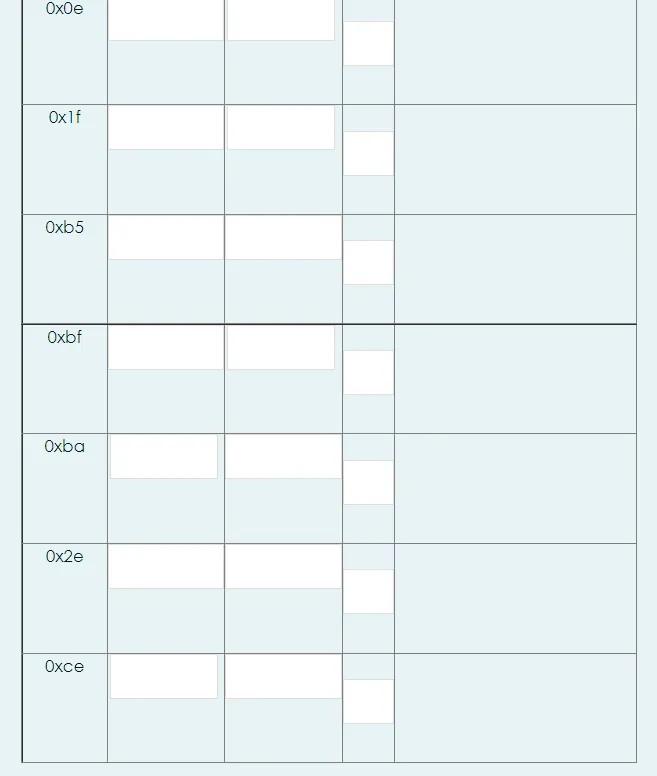

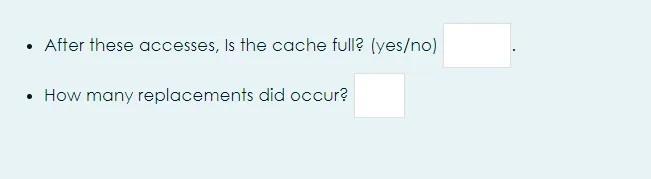

This exercise examines the effect of different cache designs, specifically comparing associative caches to the direct-mapped caches. Assume the memory is word addressing with 8-bit addresses and the cache is a fully associative cache with one word blocks and a total size of eight words. Assume one word is 32 bits. - The number of blocks in the cache is blocks. - The number of sets in the cache is set(s). - The number of blocks in the memory is blocks. - The number of tag bits in each block is bits. - The total bits required to implement the cache is bits. For this exercise, refer to the sequence of word address shown below. 0x03, 0xb4, 0x2b, 0x02, 0xbe, 0x58, 0xbf, 0x0e, 0xif, 0xb5, 0xbf, 0xba, 0x2e, 0xce Assume a true LRU replacement policy. For each reference, identify: the binary word address, the tag, whether the reference is a hit or a miss. \begin{tabular}{|c|c|l|l|l|} \hline Word Address in Hex & Word Address in Binary & Tag in Binary & Hit or Miss & Contents \\ \hline 0x03 & 00000011 & 00000011 & M & \\ \hline 0xb4 & & & & \\ \hline 0x2b & & & & \\ \hline 0x02 & & & & \\ \hline 0xbe & & & & \\ \hline 0xbf & & & & \\ \hline \end{tabular} - After these accesses, Is the cache full? (yeso) - How many replacements did occur

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started