Question: This is all the information that's given You have a system with 2 levels of cache in addition to main memory. The L1 Cache has

This is all the information that's given

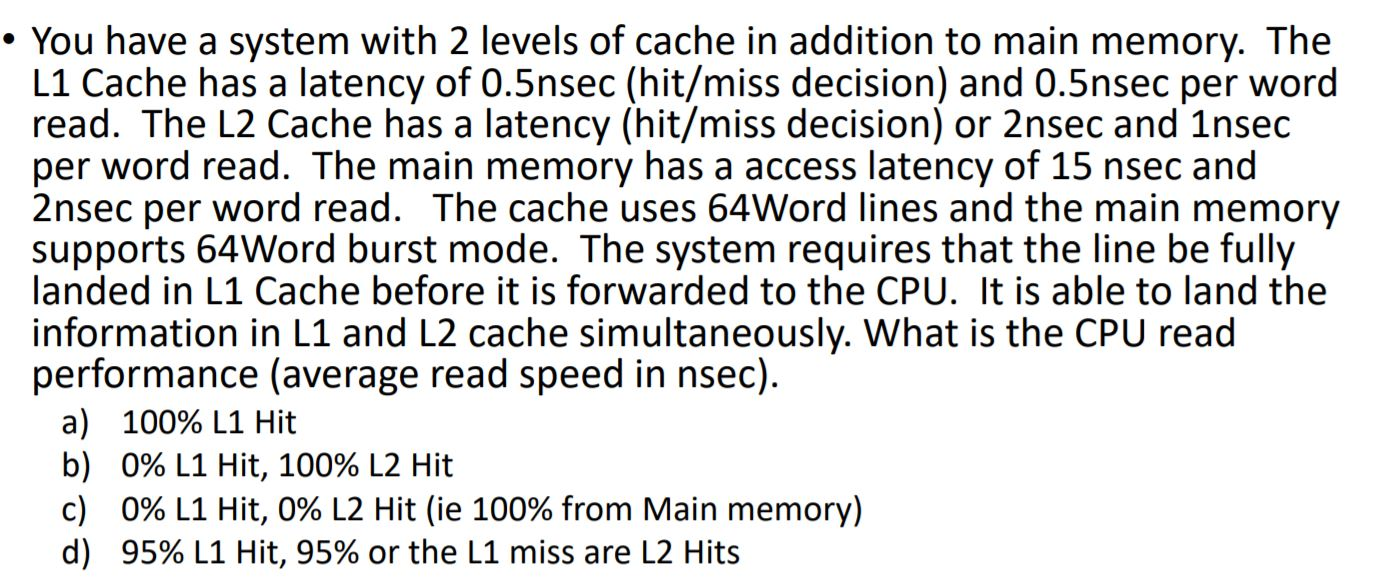

You have a system with 2 levels of cache in addition to main memory. The L1 Cache has a latency of 0.5nsec (hit/miss decision) and 0.5nsec per word read. The L2 Cache has a latency (hit/miss decision) or 2nsec and insec per word read. The main memory has a access latency of 15 nsec and 2nsec per word read. The cache uses 64Word lines and the main memory supports 64 Word burst mode. The system requires that the line be fully landed in L1 Cache before it is forwarded to the CPU. It is able to land the information in L1 and L2 cache simultaneously. What is the CPU read performance (average read speed in nsec). a) 100% L1 Hit b) 0% L1 Hit, 100% L2 Hit c) 0% L1 Hit, 0% L2 Hit (ie 100% from Main memory) d) 95% L1 Hit, 95% or the L1 miss are L2 Hits You have a system with 2 levels of cache in addition to main memory. The L1 Cache has a latency of 0.5nsec (hit/miss decision) and 0.5nsec per word read. The L2 Cache has a latency (hit/miss decision) or 2nsec and insec per word read. The main memory has a access latency of 15 nsec and 2nsec per word read. The cache uses 64Word lines and the main memory supports 64 Word burst mode. The system requires that the line be fully landed in L1 Cache before it is forwarded to the CPU. It is able to land the information in L1 and L2 cache simultaneously. What is the CPU read performance (average read speed in nsec). a) 100% L1 Hit b) 0% L1 Hit, 100% L2 Hit c) 0% L1 Hit, 0% L2 Hit (ie 100% from Main memory) d) 95% L1 Hit, 95% or the L1 miss are L2 Hits

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts