Question: This is Computer Architecture course. Please solve the following question urgently! Problem 3: (a) Use four of the 16-bit carry-lookahead adders shown in Figure 3

This is Computer Architecture course. Please solve the following question urgently!

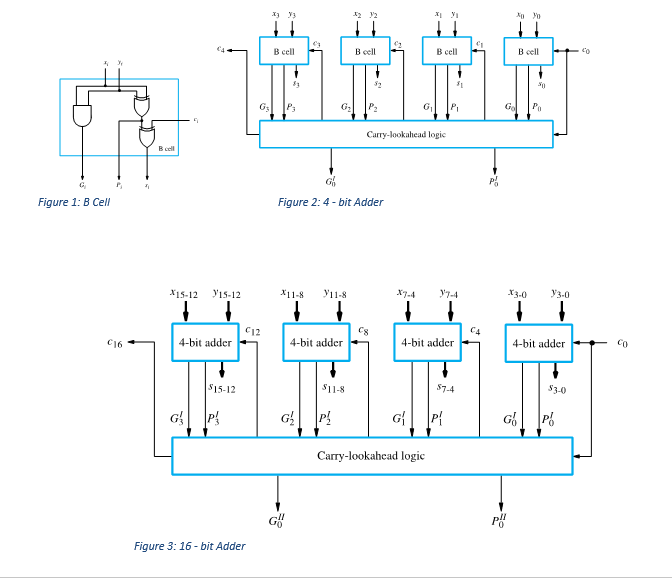

Problem 3: (a) Use four of the 16-bit carry-lookahead adders shown in Figure 3 below to design a 64 bit adder (B cell and 4 bit adder shown in Figure 1 and Figure 2 respectively) along with additional logic circuits to generate c16, c32, c48, and c64, from c0 and the GII and PII variables shown in the figure. What is the relationship of the additional logic to the logic inside circuits to the carry-lookahead logic circuits in the figure?

(b) Determine the delay through the 64-bit adder for s63 and c64.

(c) Write the expressions for G and P for each stage i.e. stages 1, 4, 16 and 64.

Y | B cell B cell B cell B cell G: Pi Gal * Carry-lookahead logic Buell G! Figure 2:4 - bit Adder Figure 1: B Cell 15+12 15-12 Vi18 | | 4-bit adder 16 4-bit adder 4-bit adder 4-bit adder C |55-12 $1-8 $7.4 53) | PL Carry-lookahead logic P Figure 3: 16-bit Adder Y | B cell B cell B cell B cell G: Pi Gal * Carry-lookahead logic Buell G! Figure 2:4 - bit Adder Figure 1: B Cell 15+12 15-12 Vi18 | | 4-bit adder 16 4-bit adder 4-bit adder 4-bit adder C |55-12 $1-8 $7.4 53) | PL Carry-lookahead logic P Figure 3: 16-bit Adder

Step by Step Solution

There are 3 Steps involved in it

To solve the problem of designing a 64bit adder using four 16bit carrylookahead adders lets break down the process into structured steps a Design a 64... View full answer

Get step-by-step solutions from verified subject matter experts