Question: This is done in vhdl, a test bench should be included too. (if not it is ok) Part 2) Implement 2's complement using Structural Modeling

This is done in vhdl, a test bench should be included too. (if not it is ok)

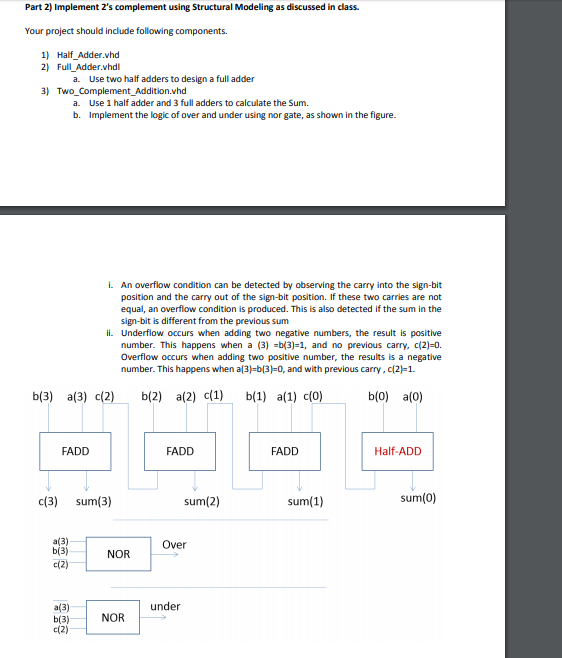

Part 2) Implement 2's complement using Structural Modeling as discussed in class Your project should include following components. 1 Half Adder.vhd 2) Full_Adder.vhdl a. Use two half adders to design a full adder 3) Two_Complement Addition.vhd Use 1 half adder and 3 full adders to calculate the Sum. Implement the logic of over and under using nor gate, as shown in the figure. a. b. i. An overflow condition can be detected by observing the carry into the sign-bit position and the carry out of the sign-bit position. If these two carries are not equal, an overflow condition is produced. This is also detected if the sum in the sign-bit is different from the previous summ ii. Underflow occurs when adding two negative numbers, the result is positive number. This happens when a (3)b(3)-1, and no previous carry, c(2)-0. Overflow occurs when adding two positive number, the results is a negative number. This happens when a(3-b(3-0, and with previous carry , c(2):1. b(3) a(3) (2) b(2) a(2) b(1) a(1) c(O) b(0) a(0) FADD FADD FADD Half-ADD c(3) sum(3) sum(2) sum(1) a(3) b(3) Over NOR al3)NOR b(3) c(2) un Part 2) Implement 2's complement using Structural Modeling as discussed in class Your project should include following components. 1 Half Adder.vhd 2) Full_Adder.vhdl a. Use two half adders to design a full adder 3) Two_Complement Addition.vhd Use 1 half adder and 3 full adders to calculate the Sum. Implement the logic of over and under using nor gate, as shown in the figure. a. b. i. An overflow condition can be detected by observing the carry into the sign-bit position and the carry out of the sign-bit position. If these two carries are not equal, an overflow condition is produced. This is also detected if the sum in the sign-bit is different from the previous summ ii. Underflow occurs when adding two negative numbers, the result is positive number. This happens when a (3)b(3)-1, and no previous carry, c(2)-0. Overflow occurs when adding two positive number, the results is a negative number. This happens when a(3-b(3-0, and with previous carry , c(2):1. b(3) a(3) (2) b(2) a(2) b(1) a(1) c(O) b(0) a(0) FADD FADD FADD Half-ADD c(3) sum(3) sum(2) sum(1) a(3) b(3) Over NOR al3)NOR b(3) c(2) un

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts