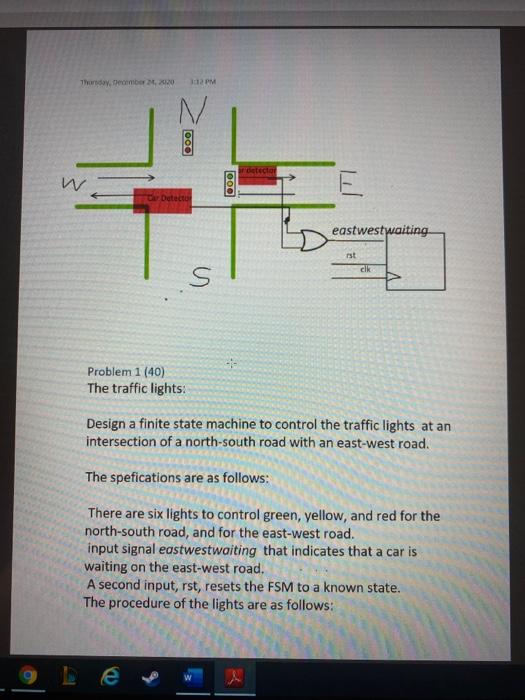

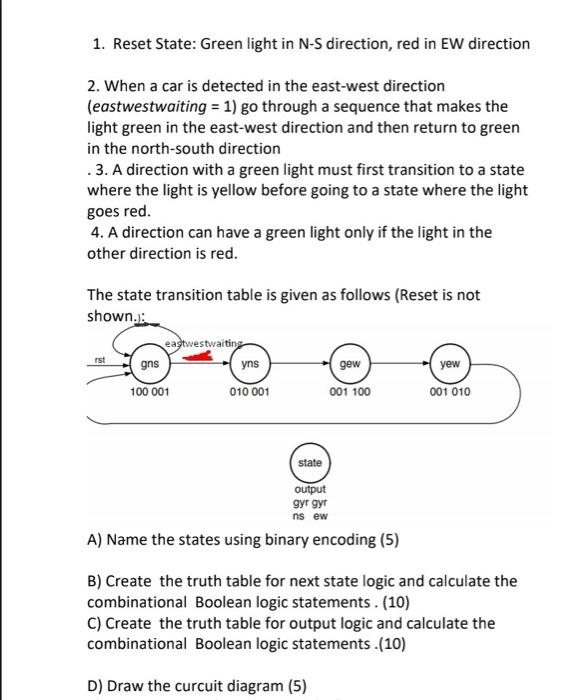

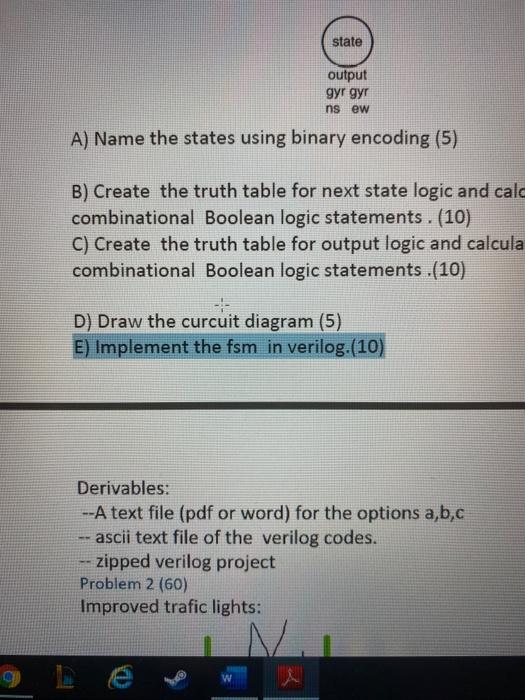

Thoday, December 2120 112 PM N. detector 000 Detecto eastwest waiting elk s Problem 1 (40) The traffic lights: Design a finite state machine to control the traffic lights at an intersection of a north-south road with an east-west road. The spefications are as follows: There are six lights to control green, yellow, and red for the north-south road, and for the east-west road. input signal eastwestwaiting that indicates that a car is waiting on the east-west road. A second input, rst, resets the FSM to a known state. The procedure of the lights are as follows: 1. Reset State: Green light in N-S direction, red in EW direction 2. When a car is detected in the east-west direction (eastwestwaiting = 1) go through a sequence that makes the light green in the east-west direction and then return to green in the north-south direction .3. A direction with a green light must first transition to a state where the light is yellow before going to a state where the light goes red. 4. A direction can have a green light only if the light in the other direction is red. The state transition table is given as follows (Reset is not shown.: rst eastwestwaiting gns yns gew yew 001 010 100 001 010 001 001 100 state output gyr gyr ns ew A) Name the states using binary encoding (5) B) Create the truth table for next state logic and calculate the combinational Boolean logic statements. (10) C) Create the truth table for output logic and calculate the combinational Boolean logic statements.(10) D) Draw the curcuit diagram (5) state output gyr gyr ns ew A) Name the states using binary encoding (5) B) Create the truth table for next state logic and calo combinational Boolean logic statements . (10) C) Create the truth table for output logic and calcula combinational Boolean logic statements .(10) D) Draw the curcuit diagram (5) E) Implement the fsm in verilog.(10) Derivables: --A text file (pdf or word) for the options a,b,c ascii text file of the verilog codes. -- zipped verilog project Problem 2 (60) Improved trafic lights: Thoday, December 2120 112 PM N. detector 000 Detecto eastwest waiting elk s Problem 1 (40) The traffic lights: Design a finite state machine to control the traffic lights at an intersection of a north-south road with an east-west road. The spefications are as follows: There are six lights to control green, yellow, and red for the north-south road, and for the east-west road. input signal eastwestwaiting that indicates that a car is waiting on the east-west road. A second input, rst, resets the FSM to a known state. The procedure of the lights are as follows: 1. Reset State: Green light in N-S direction, red in EW direction 2. When a car is detected in the east-west direction (eastwestwaiting = 1) go through a sequence that makes the light green in the east-west direction and then return to green in the north-south direction .3. A direction with a green light must first transition to a state where the light is yellow before going to a state where the light goes red. 4. A direction can have a green light only if the light in the other direction is red. The state transition table is given as follows (Reset is not shown.: rst eastwestwaiting gns yns gew yew 001 010 100 001 010 001 001 100 state output gyr gyr ns ew A) Name the states using binary encoding (5) B) Create the truth table for next state logic and calculate the combinational Boolean logic statements. (10) C) Create the truth table for output logic and calculate the combinational Boolean logic statements.(10) D) Draw the curcuit diagram (5) state output gyr gyr ns ew A) Name the states using binary encoding (5) B) Create the truth table for next state logic and calo combinational Boolean logic statements . (10) C) Create the truth table for output logic and calcula combinational Boolean logic statements .(10) D) Draw the curcuit diagram (5) E) Implement the fsm in verilog.(10) Derivables: --A text file (pdf or word) for the options a,b,c ascii text file of the verilog codes. -- zipped verilog project Problem 2 (60) Improved trafic lights