undefined

undefined

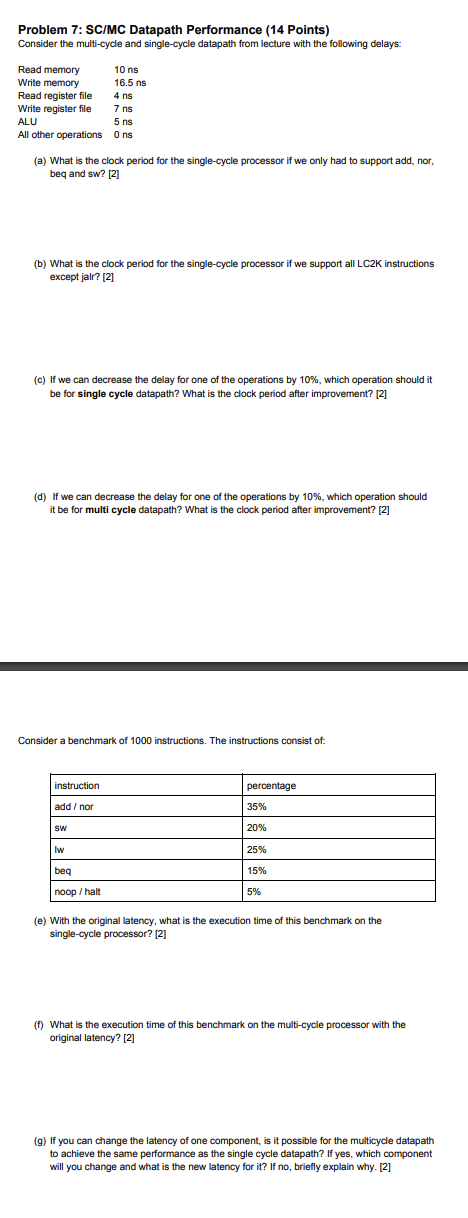

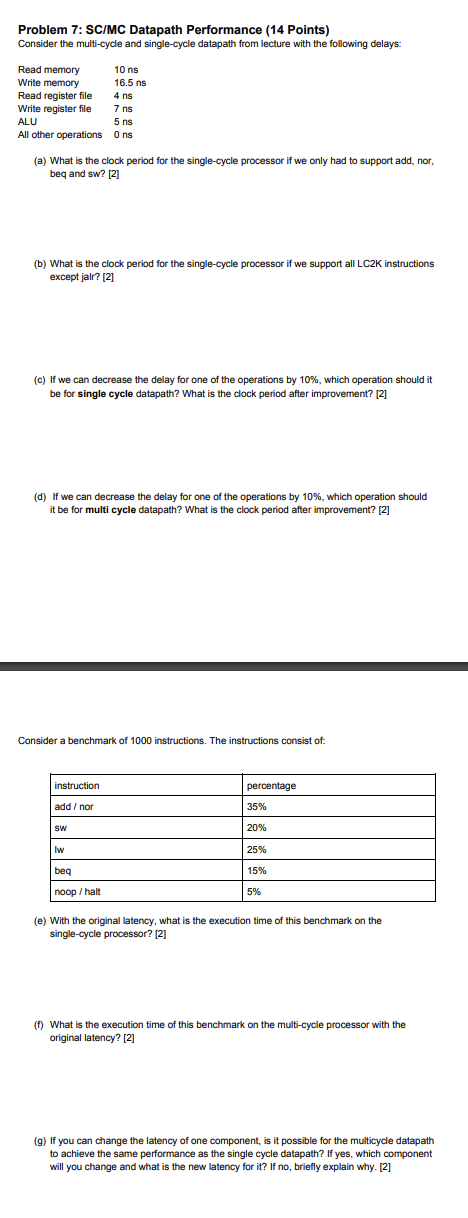

Problem 7: SC/MC Datapath Performance (14 points) Consider the multi-cycle and single-cycle datapath from lecture with the following delays: Read memory 10 ns Write memory 16.5 ns Read register file 4 ns Write register file 7 ns ALU 5 ns All other operations Ons (a) What is the clock period for the single-cycle processor if we only had to support add, nor, beq and sw? [2] (b) What is the clock period for the single-cycle processor if we support all LC2K instructions except jalr? [2] (c) If we can decrease the delay for one of the operations by 10%, which operation should it be for single cycle datapath? What is the clock period after improvement? [2] (d) If we can decrease the delay for one of the operations by 10%, which operation should it be for multi cycle datapath? What is the clock period after improvement? (2) Consider a benchmark of 1000 instructions. The instructions consist of: instruction percentage 35% add / nor SW 20% lw 25% beg 15% noop / halt 5% (e) With the original latency, what is the execution time of this benchmark on the single-cycle processor? [2] (f) What is the execution time of this benchmark on the multi-cycle processor with the original latency? [2] (9) If you can change the latency of one component, is it possible for the multicycle datapath to achieve the same performance as the single cycle datapath? If yes, which component will you change and what is the new latency for it? If no, briefly explain why. [2] Problem 7: SC/MC Datapath Performance (14 points) Consider the multi-cycle and single-cycle datapath from lecture with the following delays: Read memory 10 ns Write memory 16.5 ns Read register file 4 ns Write register file 7 ns ALU 5 ns All other operations Ons (a) What is the clock period for the single-cycle processor if we only had to support add, nor, beq and sw? [2] (b) What is the clock period for the single-cycle processor if we support all LC2K instructions except jalr? [2] (c) If we can decrease the delay for one of the operations by 10%, which operation should it be for single cycle datapath? What is the clock period after improvement? [2] (d) If we can decrease the delay for one of the operations by 10%, which operation should it be for multi cycle datapath? What is the clock period after improvement? (2) Consider a benchmark of 1000 instructions. The instructions consist of: instruction percentage 35% add / nor SW 20% lw 25% beg 15% noop / halt 5% (e) With the original latency, what is the execution time of this benchmark on the single-cycle processor? [2] (f) What is the execution time of this benchmark on the multi-cycle processor with the original latency? [2] (9) If you can change the latency of one component, is it possible for the multicycle datapath to achieve the same performance as the single cycle datapath? If yes, which component will you change and what is the new latency for it? If no, briefly explain why. [2]

undefined

undefined