Answered step by step

Verified Expert Solution

Question

1 Approved Answer

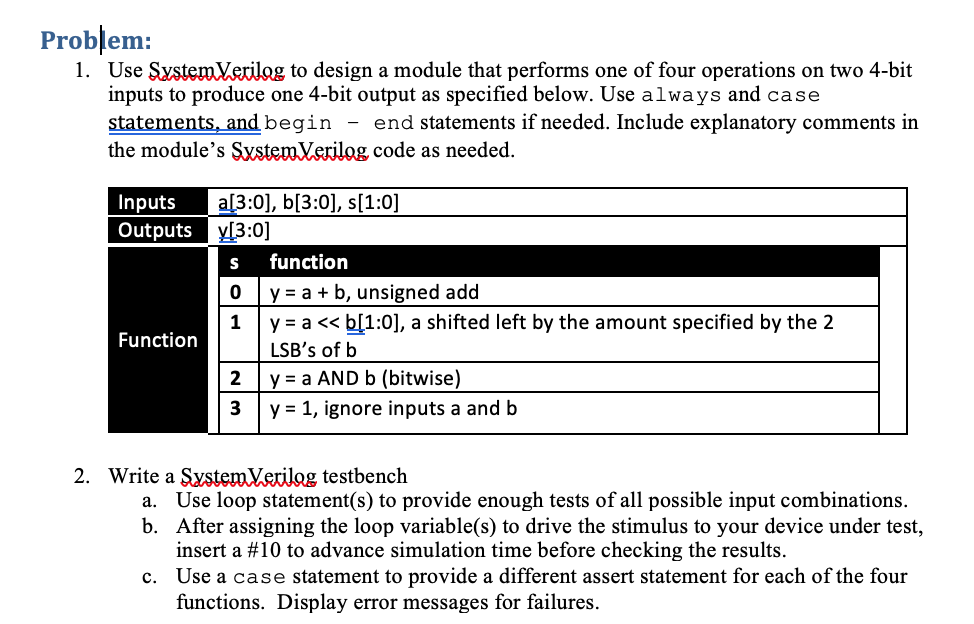

Use SystemVerilog to design a module that performs one of four operations on two 4-bit inputs to produce one 4-bit output as specified below. Use

- Use SystemVerilog to design a module that performs one of four operations on two 4-bit inputs to produce one 4-bit output as specified below. Use alwaysand case statements, and begin endstatements if needed. Include explanatory comments in the modules SystemVerilog code as needed.

- Write a SystemVerilog testbench

- Use loop statement(s) to provide enough tests of all possible input combinations.

- After assigning the loop variable(s) to drive the stimulus to your device under test, insert a #10 to advance simulation time before checking the results.

- Use a casestatement to provide a different assert statement for each of the four functions. Display error messages for failures.

Problem: 1. Use SxstemVerilog to design a module that performs one of four operations on two 4-bit inputs to produce one 4-bit output as specified below. Use always and case statements, and begin - end statements if needed. Include explanatory comments in the module's Systemerilag code as needed. Inputs Outputs y3:0] al3:0], b[3:0], s[1:0] s function o y-a +b, unsigned add 1y a

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started