Answered step by step

Verified Expert Solution

Question

1 Approved Answer

use verilog and create testbench. D Latch: A flip-flop captures data at its input at a clock's positive or negative edge. The important thing to

use verilog and create testbench.

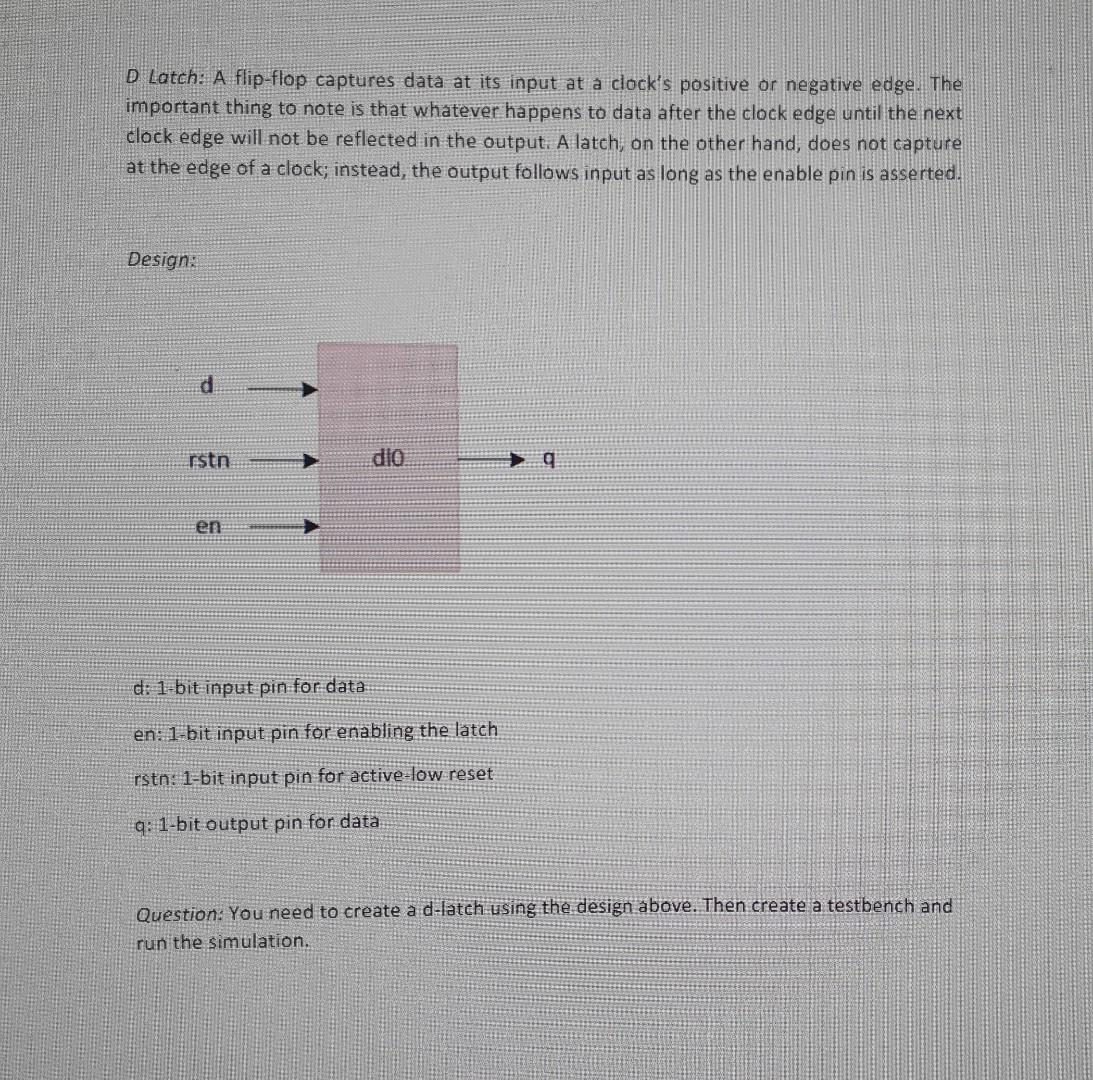

D Latch: A flip-flop captures data at its input at a clock's positive or negative edge. The important thing to note is that whatever happens to data after the clock edge until the next clock edge will not be reflected in the output. A latch, on the other hand, does not capture at the edge of a clock; instead, the output follows input as long as the enable pin is asserted. Design: d: 1-bit input pin for data en: 1 -bit input pin for enabling the latch rstn: 1-bit input pin for active-low reset 9:1-bit output pin for data Question: You need to create a d-fatch using the design above. Then create a testbench and run the simulationStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started