Question

Use VHDL to build a structural counter. The state of the counter should be incremented only once for each clock cycle if the enable input

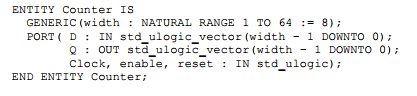

Use VHDL to build a structural counter. The state of the counter should be incremented only once for each clock cycle if the enable input is asserted (1). You will also need to include a synchronous reset mechanism that initializes the counter to the input value when the reset input is asserted (1). The value of the enable input does not matter if the reset is asserted. When the reset input is deasserted (0) the counter should increment with each clock cycle when the enable is asserted. If neither the reset nor the enable is asserted, then the counter state does not change. Here is the entity declaration for counter:

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started