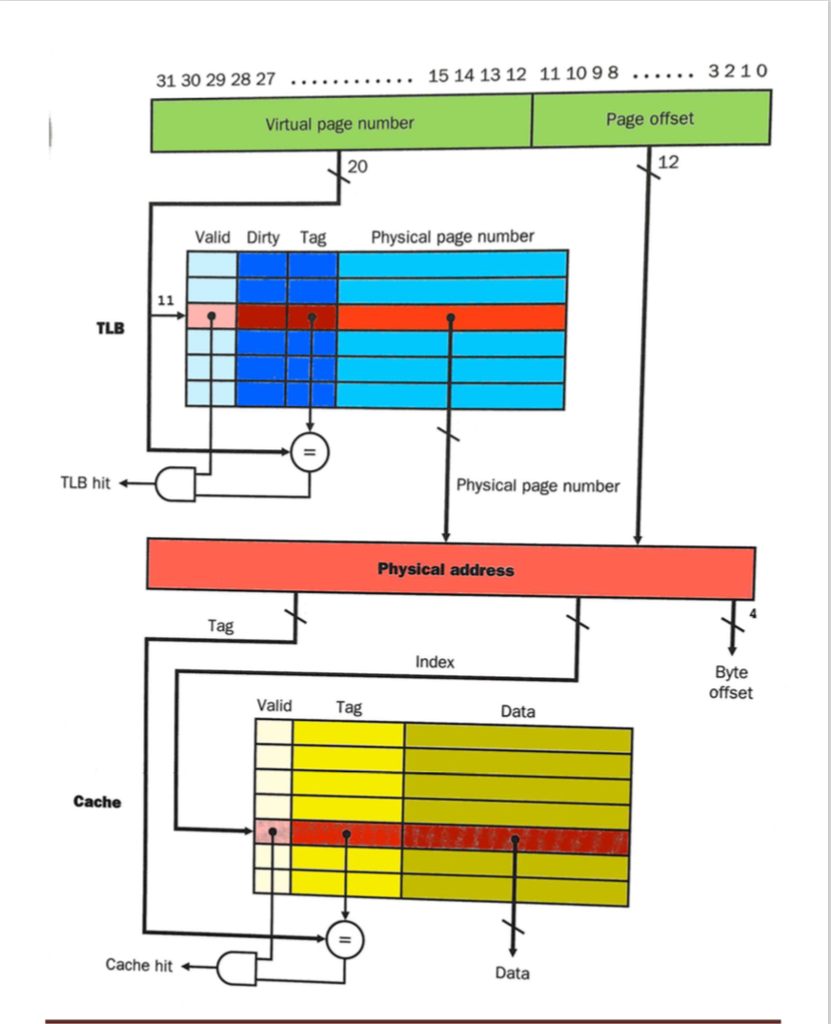

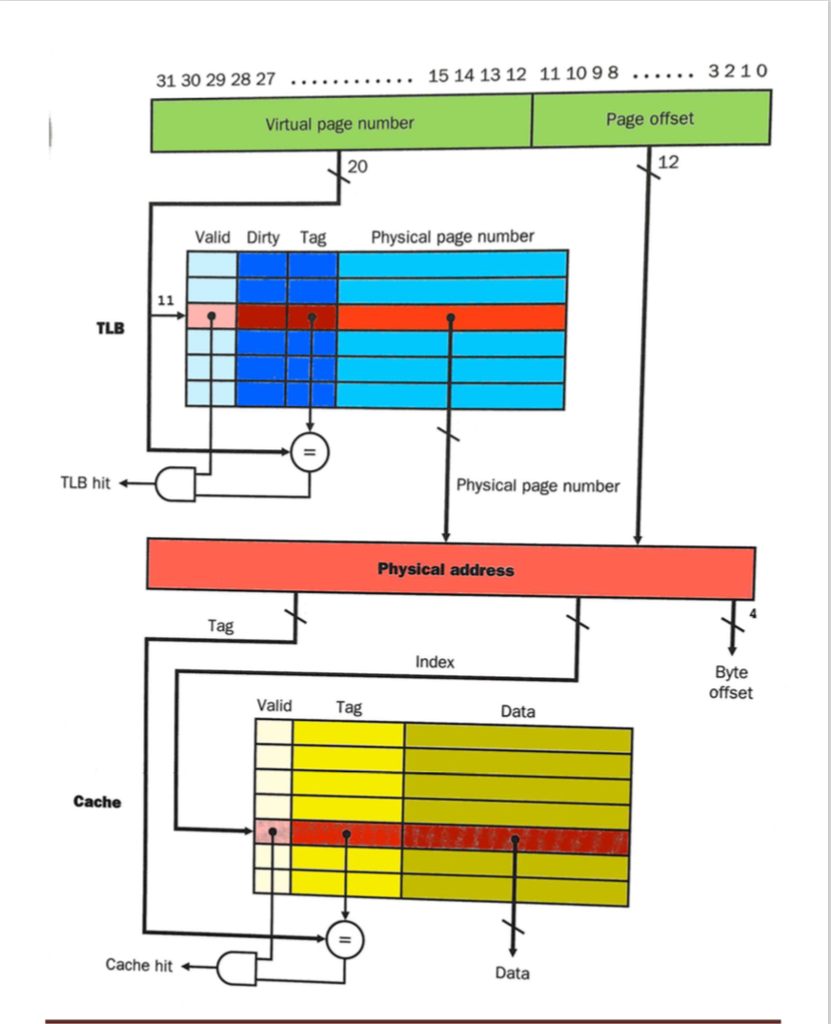

Using the Virtual Memory Caching diagram provided, plus the information given below, answer the following questions. Please, do not mark on the diagram and retum it at the end of the exam. You may express any answer as a power of 2 if applicable. Also, unlike the diagram, our TLB is 4-way Set Associative and our cache is 2- way set associative. In all cases, best to briefly show how you arrived at your answer better partial credit 4. Given: 32-bit virtual memory, 4 KB page size, 32 GB of physical memory, index for the TLB is bits For the cache, the tag has 17 bits and the byte offset is 4 bits. a. (2 pts) How many bits in the physical memory address? b. (2 pts) How many indices in the TLB? C. (2 pts) How many bits in the TLB tag? d. (2 pts) How may bits in the TLB physical page number? (8 pts) How many bytes are required to implement our 4-way set associative TLB? Include 1 valid bit, 1 dirty bit, and 2 protection bits e. f. (2 pts) What kind of logic gate would make a good comparator to compare the tag in the TLB with the virtual address bits to determine a TLB hit. Output is high if they match g (4 pts) IF the page table were to be implemented as an array with one entry for every virtual address, is there still an advantage to using a TLB? Why or why not? (Guessing "yes" or "no" gets no points.) h. (2 pts) How many bits in the index into the cache from the physical address? Using the Virtual Memory Caching diagram provided, plus the information given below, answer the following questions. Please, do not mark on the diagram and retum it at the end of the exam. You may express any answer as a power of 2 if applicable. Also, unlike the diagram, our TLB is 4-way Set Associative and our cache is 2- way set associative. In all cases, best to briefly show how you arrived at your answer better partial credit 4. Given: 32-bit virtual memory, 4 KB page size, 32 GB of physical memory, index for the TLB is bits For the cache, the tag has 17 bits and the byte offset is 4 bits. a. (2 pts) How many bits in the physical memory address? b. (2 pts) How many indices in the TLB? C. (2 pts) How many bits in the TLB tag? d. (2 pts) How may bits in the TLB physical page number? (8 pts) How many bytes are required to implement our 4-way set associative TLB? Include 1 valid bit, 1 dirty bit, and 2 protection bits e. f. (2 pts) What kind of logic gate would make a good comparator to compare the tag in the TLB with the virtual address bits to determine a TLB hit. Output is high if they match g (4 pts) IF the page table were to be implemented as an array with one entry for every virtual address, is there still an advantage to using a TLB? Why or why not? (Guessing "yes" or "no" gets no points.) h. (2 pts) How many bits in the index into the cache from the physical address