Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Very very urgent Please answer 2 This question is about mechanisms for increasing CPU efficiency (a) Consider an ARM CPU_that uses 32-bit addresses and is

Very very urgent Please answer

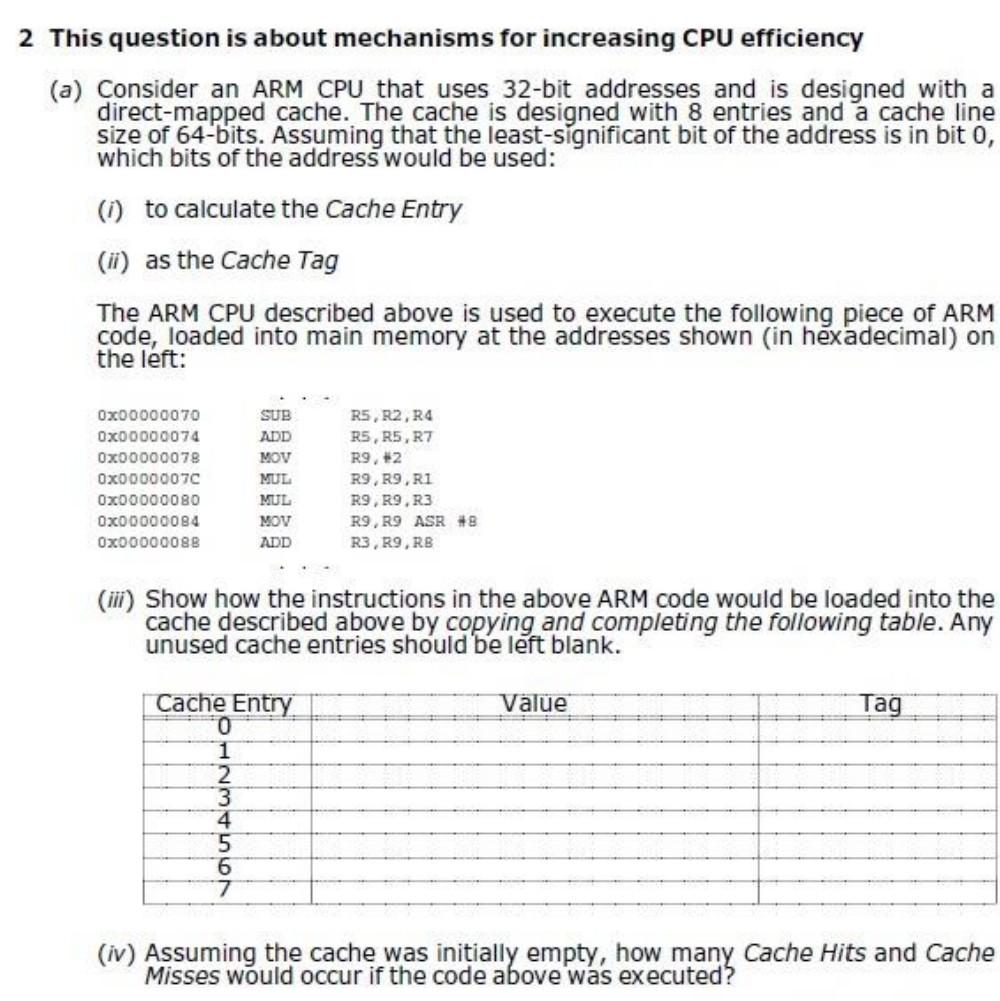

2 This question is about mechanisms for increasing CPU efficiency (a) Consider an ARM CPU_that uses 32-bit addresses and is designed with a direct-mapped cache. The cache is designed with 8 entries and a cache line size of 64-bits. Assuming that the least-sgnificant bit of the address is in bit 0, which bits of the address would be used: (1) to calculate the Cache Entry (ii) as the Cache Tag The ARM CPU described above is used to execute the following piece of ARM code, loaded into main memory at the addresses shown in hexadecimal) on the left: Ox00000070 Ox00000074 Ox00000078 Ox00000070 Ox00000080 OX00000084 Ox00000088 SUB ADD MOV MUL MUL MOV ADD R5, R2,R4 RS, R5, R7 R9, #2 R9, R9, R1 R9 R9, R3 R9, R9 ASR #8 R3, R9, RB (ii) Show how the instructions in the above ARM code would be loaded into the cache described above by copying and completing the following table. Any unused cache entries should be left blank. Value Tag Cache Entry 0 1 2 4 5 6 (iv) Assuming the cache was initially empty, how many Cache Hits and Cache Misses would occur if the code above was executed? 2 This question is about mechanisms for increasing CPU efficiency (a) Consider an ARM CPU_that uses 32-bit addresses and is designed with a direct-mapped cache. The cache is designed with 8 entries and a cache line size of 64-bits. Assuming that the least-sgnificant bit of the address is in bit 0, which bits of the address would be used: (1) to calculate the Cache Entry (ii) as the Cache Tag The ARM CPU described above is used to execute the following piece of ARM code, loaded into main memory at the addresses shown in hexadecimal) on the left: Ox00000070 Ox00000074 Ox00000078 Ox00000070 Ox00000080 OX00000084 Ox00000088 SUB ADD MOV MUL MUL MOV ADD R5, R2,R4 RS, R5, R7 R9, #2 R9, R9, R1 R9 R9, R3 R9, R9 ASR #8 R3, R9, RB (ii) Show how the instructions in the above ARM code would be loaded into the cache described above by copying and completing the following table. Any unused cache entries should be left blank. Value Tag Cache Entry 0 1 2 4 5 6 (iv) Assuming the cache was initially empty, how many Cache Hits and Cache Misses would occur if the code above was executedStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started