Answered step by step

Verified Expert Solution

Question

1 Approved Answer

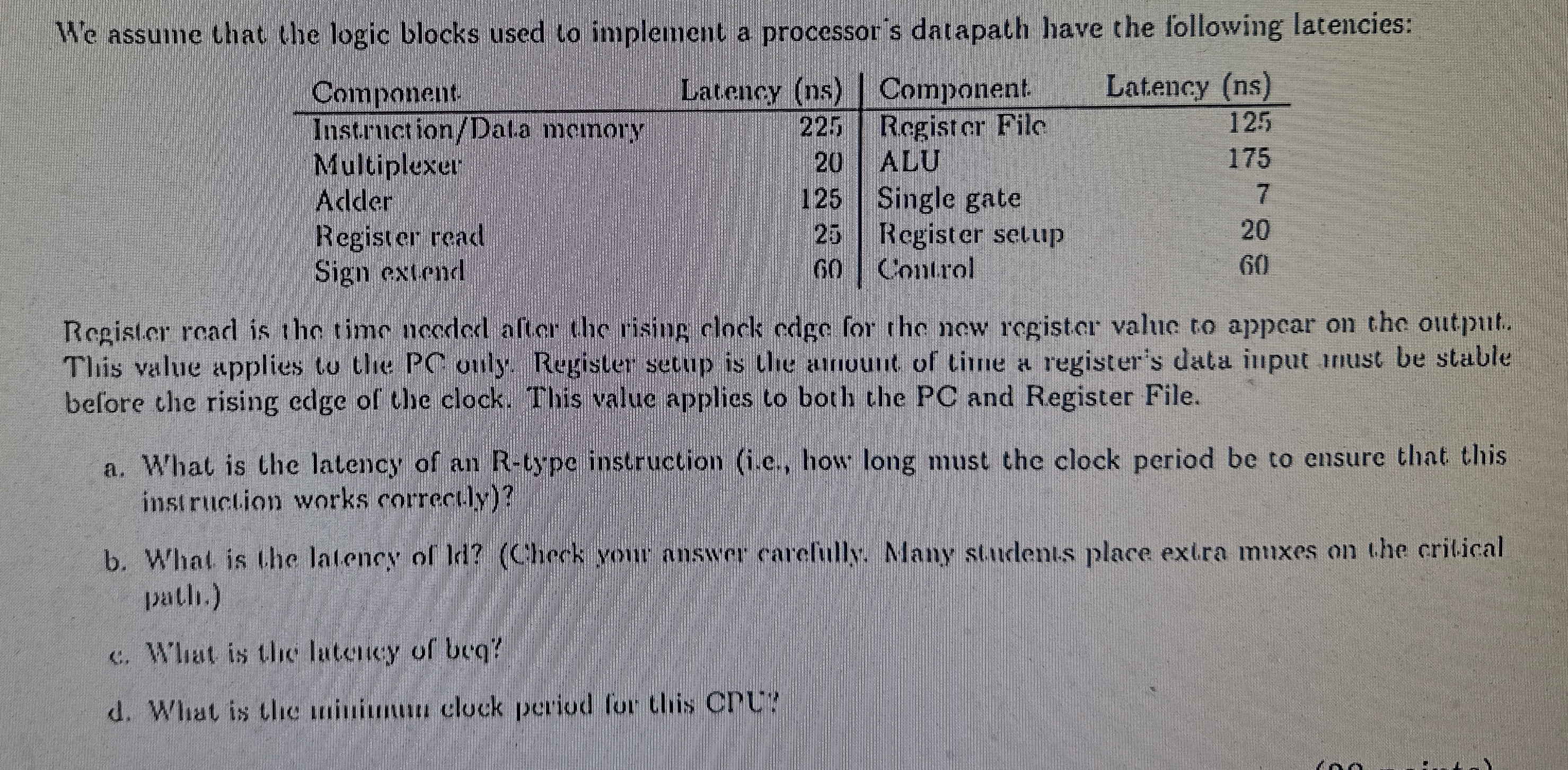

We assume that the logic blocks used to implement a processor's datapath have the following latencies: table [ [ Component , Latency ( ns

We assume that the logic blocks used to implement a processor's datapath have the following latencies:

tableComponentLatency nsComponent.,Latency nsInstrrnctionDala meinory,Register File,MultiplexerALU,AdderSingle gate,Register read,Register setup,Sign extend,Comtrol,

Register read is the time necded after the rising clock edge for the new register value to appear on the out.put. This value applies to the PC only. Register setup is the annuut of time a register's data input must be stable before the rising edge of the clock. This value applies to both the PC and Register File.

a What is the latency of an Rtype instruction ie how long must the clock period be to ensure that this instruction works correctly

b What is the latency of ldCheck your answer carelully: Many students place extra muxes on the critical path.

c What is the latericy of beq?

d What is the minimum cluck period for this CPU?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started