Question

We decide to use processor A from the previous problem to do oating-point arithmetic. Were considering two approaches. (1) We could write the oating point

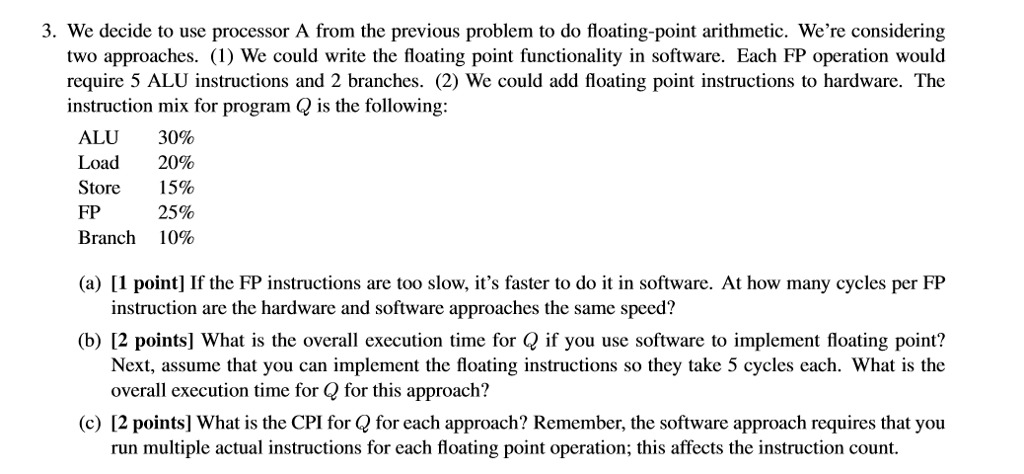

We decide to use processor A from the previous problem to do oating-point arithmetic. Were considering two approaches. (1) We could write the oating point functionality in software. Each FP operation would require 5 ALU instructions and 2 branches. (2) We could add oating point instructions to hardware. The instruction mix for program Q is the following:

ALU 30% Load 20% Store 15% FP 25% Branch 10%

If the FP instructions are too slow, its faster to do it in software. At how many cycles per FP instruction are the hardware and software approaches the same speed?

What is the overall execution time for Q if you use software to implement oating point? Next, assume that you can implement the oating instructions so they take 5 cycles each. What is the overall execution time for Q for this approach?

What is the CPI for Q for each approach? Remember,the software approach requires that you run multiple actual instructions for each oating point operation; this affects the instruction count.

3. We decide to use processor A from the previous problem to do floating-point arithmetic. We're considering two approaches. (1) We could write the floating point functionality in software. Each FP operation would require 5 ALU instructions and 2 branches. (2) We could add floating point instructions to hardware. The instruction mix for program Q is the following: ALU 30% Load 20% Store 15% FP 25% Branch 10% (a) [1 point] If the FP instructions are too slow, it's faster to do it in software. At how many cycles per FP instruction are the hardware and software approaches the same speed? (b) [2 points] What is the overall execution time for Q if you use software to implement floating point? Next, assume that you can implement the floating instructions so they take 5 cycles cach. What is the overall execution time for Q for this approach? (c) [2 points] What is the CPI for for each approach? Remember, the software approach requires that you run multiple actual instructions for each floating point operation; this affects the instruction count. 3. We decide to use processor A from the previous problem to do floating-point arithmetic. We're considering two approaches. (1) We could write the floating point functionality in software. Each FP operation would require 5 ALU instructions and 2 branches. (2) We could add floating point instructions to hardware. The instruction mix for program Q is the following: ALU 30% Load 20% Store 15% FP 25% Branch 10% (a) [1 point] If the FP instructions are too slow, it's faster to do it in software. At how many cycles per FP instruction are the hardware and software approaches the same speed? (b) [2 points] What is the overall execution time for Q if you use software to implement floating point? Next, assume that you can implement the floating instructions so they take 5 cycles cach. What is the overall execution time for Q for this approach? (c) [2 points] What is the CPI for for each approach? Remember, the software approach requires that you run multiple actual instructions for each floating point operation; this affects the instruction count

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started