Question

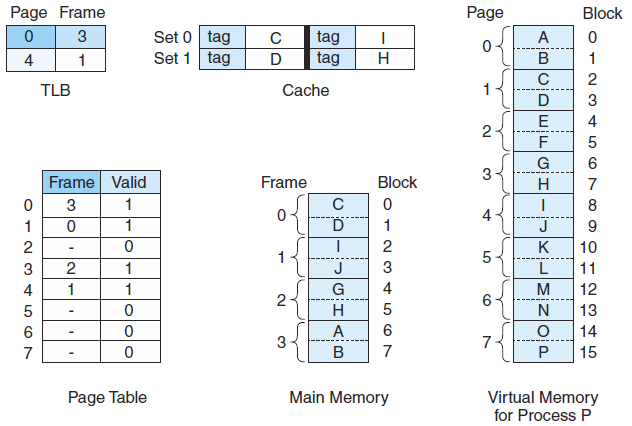

We have a virtual memory system with a two-entry TLB, a 2-way set associative cache, and a page table for a process P. Assume the

We have a virtual memory system with a two-entry TLB, a 2-way set associative cache, and a page table for a process P. Assume the size of cache blocks is 8 bytes (i.e. one cache block includes 8 bytes) and the size of virtual page size is 16 bytes (i.e. one virtual page includes 16 bytes).

In the system below, main memory is divided into blocks, where each block is represented by a letter. The exact byte in each block is represented by the letter with a number, e.g. 8 bytes stored in letter D are D0,D1,D2,D3,D4,D5,D6 and D7 (i.e. the 1st byte in D is D0, the 2nd byte in D is D1, ..., the 8th byte in D is D7). Two blocks equal one page frame.

a) How many bits are in a virtual address for process P (i.e. how long is the

virtual address width)?

b) How many bits are in a physical address (i.e. how long is the physical

memory address width)?

c) Show the address format for virtual address 24 (decimal) (specify field

name and size) that would be used by the system to translate to a physical

address and then translate this virtual address into the corresponding

physical address (i.e. giving its corresponding physical address), and then

give the value stored at memory that fetched by virtual address 24

(decimal)

BI 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 2 3 5 6 01234567 CD-JGHAB M 2 3 Fr 2 0 1 30-21- 01234567 BI 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 2 3 5 6 01234567 CD-JGHAB M 2 3 Fr 2 0 1 30-21- 01234567Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started