Question: what do you mean--no code?? Step 2: Write the code for a 2:1 multiplexer mux4 mux_in_a[3:0] mux_in_b[3:0] mux_sel mux_out[3:0] 1. Create a VHDL file using

what do you mean--no code??

what do you mean--no code??

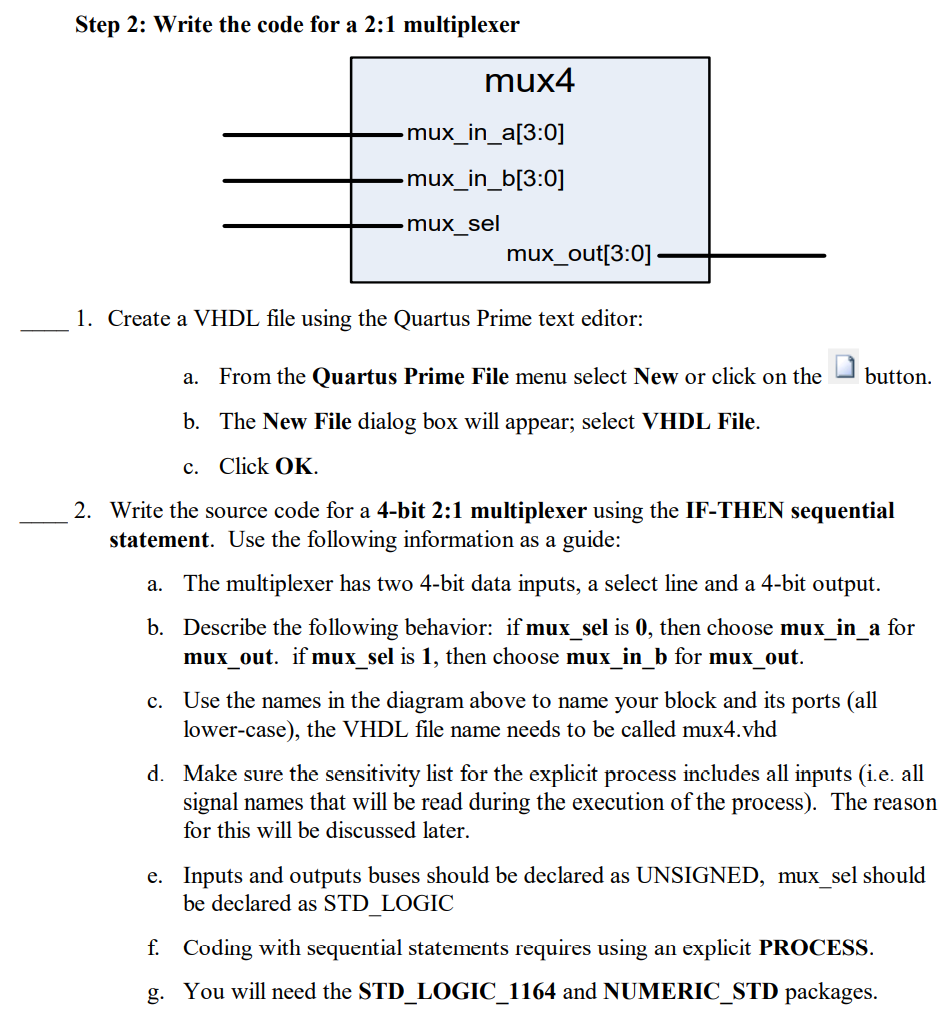

Step 2: Write the code for a 2:1 multiplexer mux4 mux_in_a[3:0] mux_in_b[3:0] mux_sel mux_out[3:0] 1. Create a VHDL file using the Quartus Prime text editor: a. From the Quartus Prime File menu select New or click on the button. b. The New File dialog box will appear; select VHDL File. c. Click OK 2. Write the source code for a 4-bit 2:1 multiplexer using the IF-THEN sequential statement. Use the following information as a guide: a. The multiplexer has two 4-bit data inputs, a select line and a 4-bit output. b. Describe the following behavior: if mux_sel is 0, then choose mux_in_a for mux__ out. if mux sel is 1, then choose mux in b for mux out. c. Use the names in the diagram above to name your block and its ports (all lower-case), the VHDL file name needs to be called mux4.vhd d. Make sure the sensitivity list for the explicit process includes all inputs (i.e. all signal names that will be read during the execution of the process). The reason for this will be discussed later. are e. Inputs and outputs ises should be declared as STD LOGIC as UNSIGNED, mux_sel should f. Coding with sequential statements requires using an explicit PROCESS. g. You will need the STD_LOGIC_1164 and NUMERIC_STD packages. Step 2: Write the code for a 2:1 multiplexer mux4 mux_in_a[3:0] mux_in_b[3:0] mux_sel mux_out[3:0] 1. Create a VHDL file using the Quartus Prime text editor: a. From the Quartus Prime File menu select New or click on the button. b. The New File dialog box will appear; select VHDL File. c. Click OK 2. Write the source code for a 4-bit 2:1 multiplexer using the IF-THEN sequential statement. Use the following information as a guide: a. The multiplexer has two 4-bit data inputs, a select line and a 4-bit output. b. Describe the following behavior: if mux_sel is 0, then choose mux_in_a for mux__ out. if mux sel is 1, then choose mux in b for mux out. c. Use the names in the diagram above to name your block and its ports (all lower-case), the VHDL file name needs to be called mux4.vhd d. Make sure the sensitivity list for the explicit process includes all inputs (i.e. all signal names that will be read during the execution of the process). The reason for this will be discussed later. are e. Inputs and outputs ises should be declared as STD LOGIC as UNSIGNED, mux_sel should f. Coding with sequential statements requires using an explicit PROCESS. g. You will need the STD_LOGIC_1164 and NUMERIC_STD packages

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts