Will thumb up for correct answer!

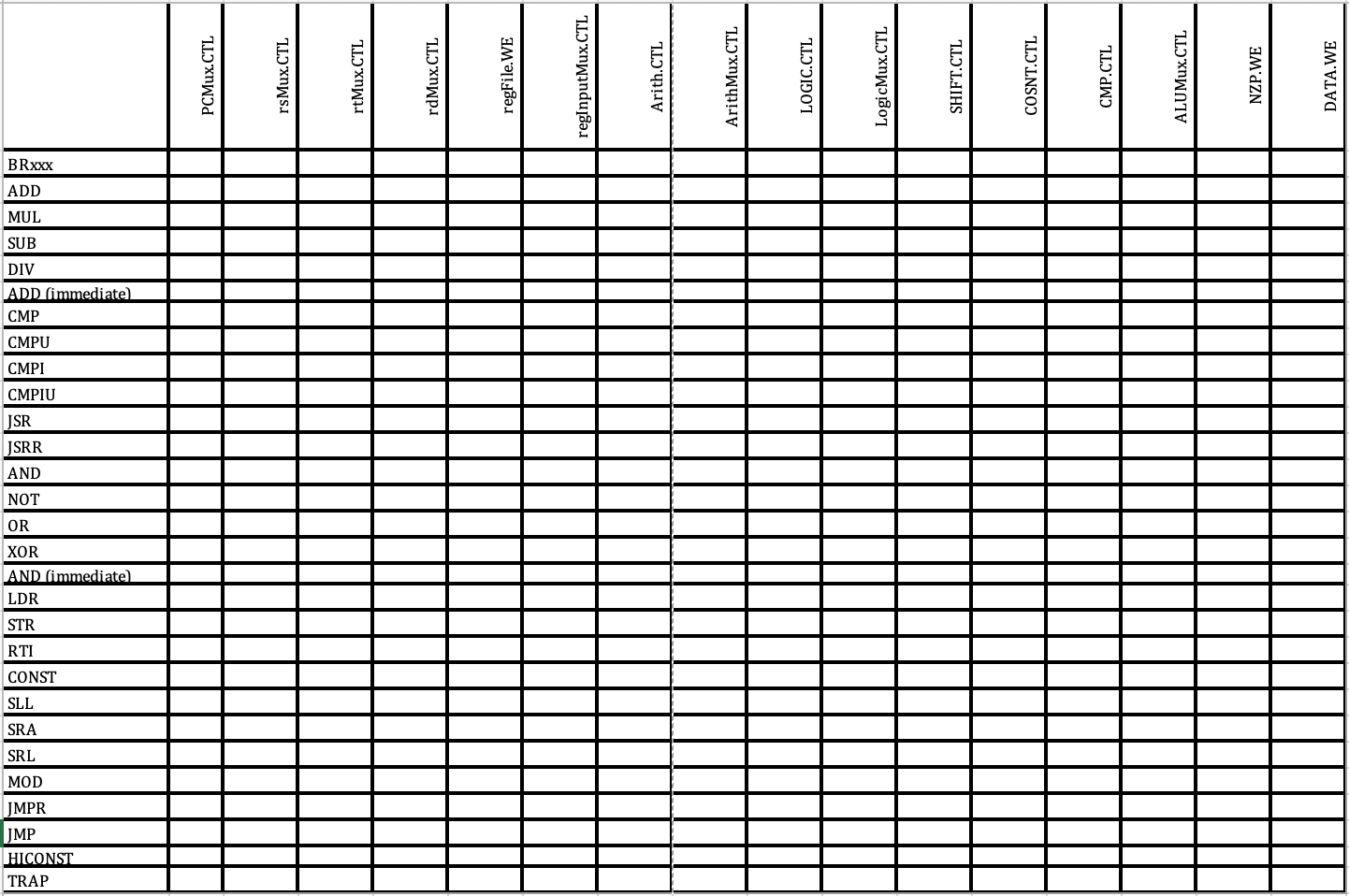

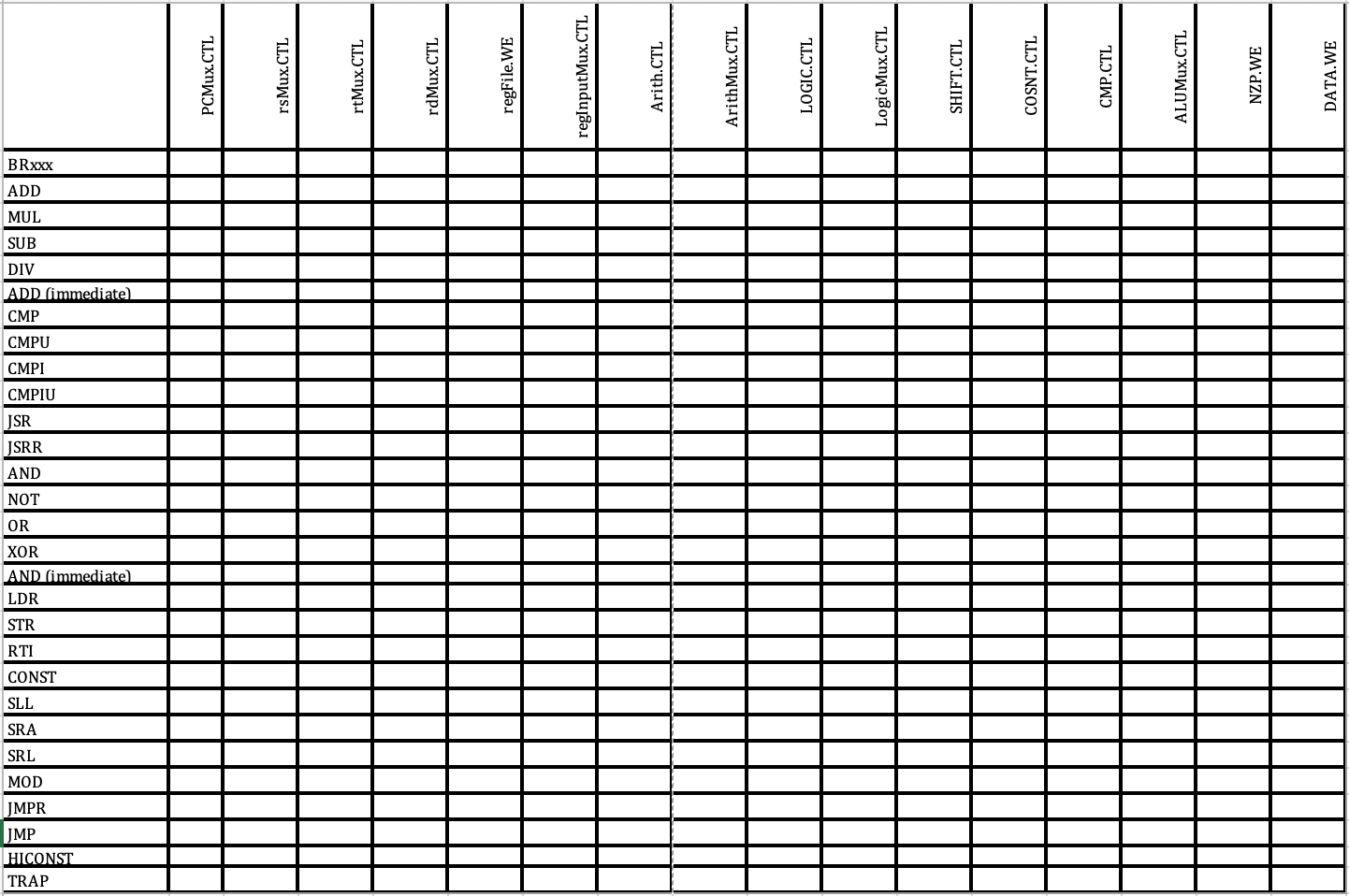

Fill this form:

Reference:

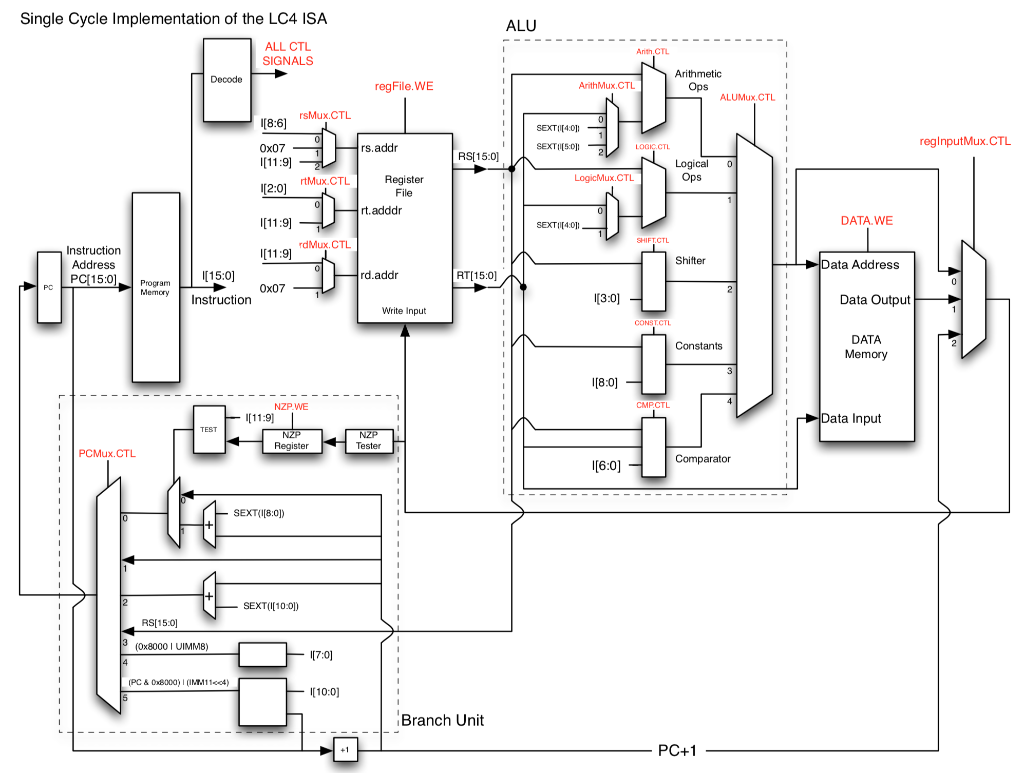

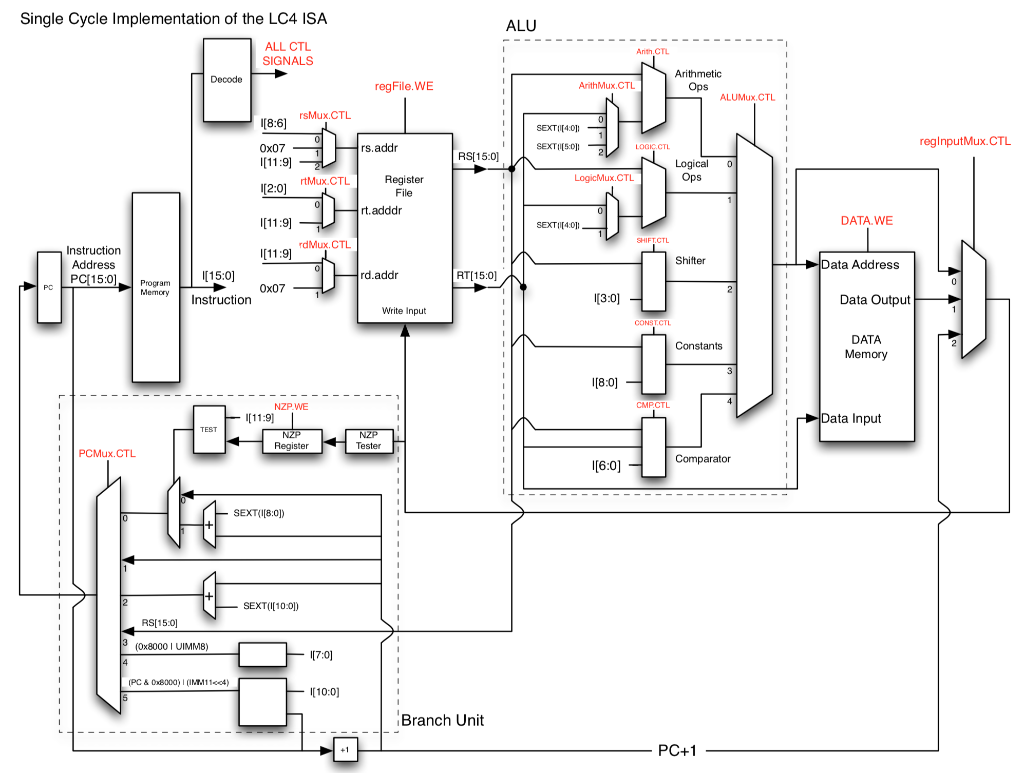

TRAP JMP HICONST JMPR MOD SRL SRA SLL CONST RTI STR LDR XOR OR NOT AND JSRR JSR CMPIU CMPI CMPU CMP DIV SUB MUL ADD BRxxx AND immediate) ADD fimmediate PCMux.CTL rs Mux.CTL rtMux.CTL rd Mux.CTL regFile. WE reginputMux.CTL Arith.CTL LI SLSLS LLLLLLLL --- ArithMux.CTL LOGIC.CTL LogicMux.CTL SHIFT.CTL COSNT.CTL CMP.CTL ALUMux.CTL NZP.WE DATA.WE ALU Single Cycle Implementation of the LC4 ISA ALL CTL SIGNALS Decode Arith.CTL regFile.WE ArithMux.CTL Arithmetic Ops ALUMUX.CTL 1[8:6] Mux.CTL SEXTI[4:01 - rs.addr SEXT|[5:01 regInputMux.CTL Ox07 [11:9) RS(15:0) 0 Logical Ops LogicMux.CTL 1/2:07 MUX.CTL Register File rt.adddr [11:9] SEXT|[4:01 DATA.WE SHIFT.CTL 1[11:9) TaMwX.CTL Shifter Instruction Address PO! PC(15:0) Data Address rd.addr RT(15:0] Program Memory [15:0) Instruction 0x07 JIH [3:0) Data Output Write Input CONST.CTL Constants DATA Memory 294 1[8:0] + - - - - - - - NZP.WE CMPCTL Data Input PCMux.CTL 1[6:0] Comparator --------------------- SEXTI[8:03) - SEXT([10:0) RS[15:01 3 (0x8000 I VIMMB) 17:01 (PC & 0x8000) (IMM11004) [10:0) Branch Unit - PC+1 TRAP JMP HICONST JMPR MOD SRL SRA SLL CONST RTI STR LDR XOR OR NOT AND JSRR JSR CMPIU CMPI CMPU CMP DIV SUB MUL ADD BRxxx AND immediate) ADD fimmediate PCMux.CTL rs Mux.CTL rtMux.CTL rd Mux.CTL regFile. WE reginputMux.CTL Arith.CTL LI SLSLS LLLLLLLL --- ArithMux.CTL LOGIC.CTL LogicMux.CTL SHIFT.CTL COSNT.CTL CMP.CTL ALUMux.CTL NZP.WE DATA.WE ALU Single Cycle Implementation of the LC4 ISA ALL CTL SIGNALS Decode Arith.CTL regFile.WE ArithMux.CTL Arithmetic Ops ALUMUX.CTL 1[8:6] Mux.CTL SEXTI[4:01 - rs.addr SEXT|[5:01 regInputMux.CTL Ox07 [11:9) RS(15:0) 0 Logical Ops LogicMux.CTL 1/2:07 MUX.CTL Register File rt.adddr [11:9] SEXT|[4:01 DATA.WE SHIFT.CTL 1[11:9) TaMwX.CTL Shifter Instruction Address PO! PC(15:0) Data Address rd.addr RT(15:0] Program Memory [15:0) Instruction 0x07 JIH [3:0) Data Output Write Input CONST.CTL Constants DATA Memory 294 1[8:0] + - - - - - - - NZP.WE CMPCTL Data Input PCMux.CTL 1[6:0] Comparator --------------------- SEXTI[8:03) - SEXT([10:0) RS[15:01 3 (0x8000 I VIMMB) 17:01 (PC & 0x8000) (IMM11004) [10:0) Branch Unit - PC+1