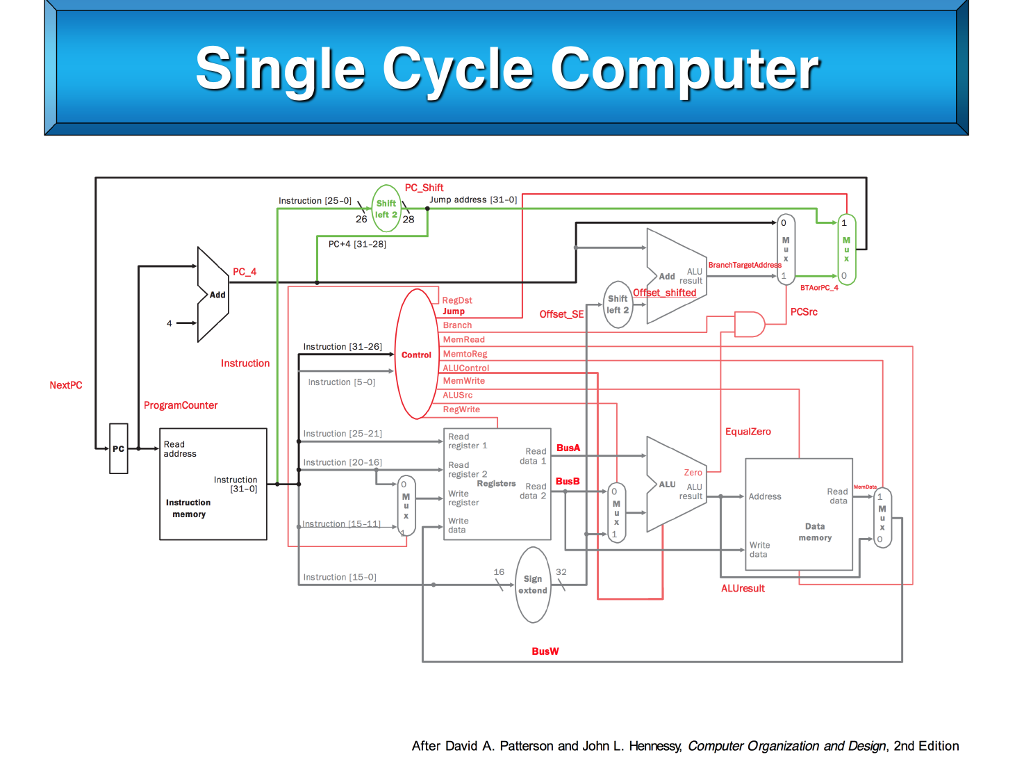

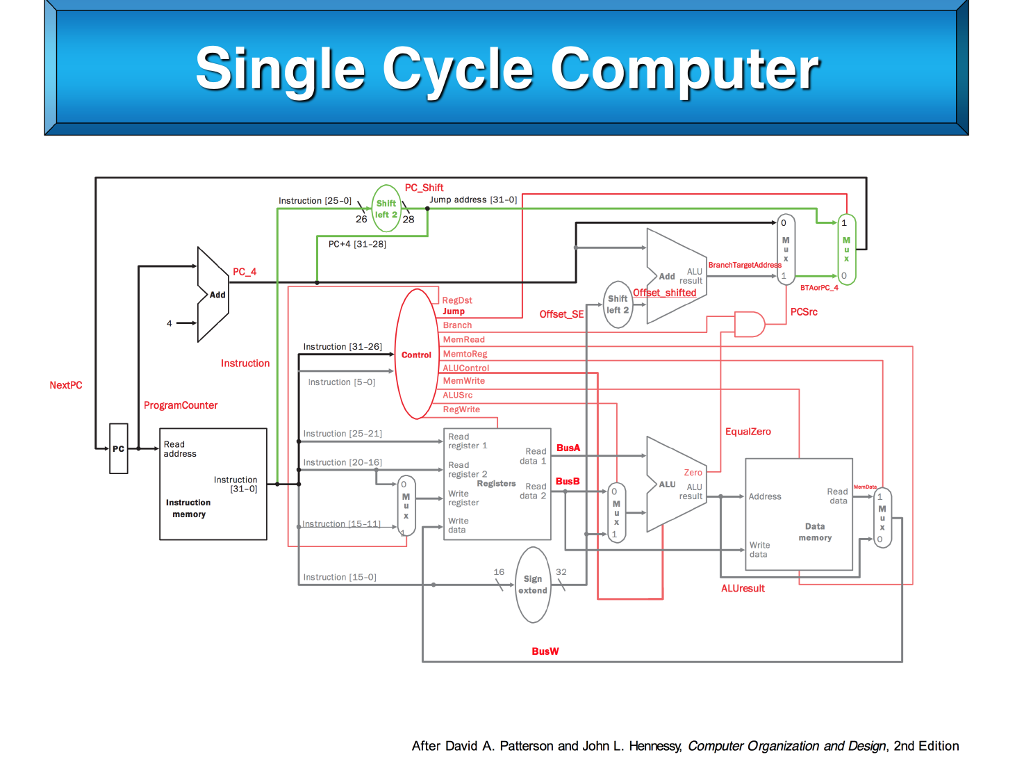

Write the Verilog which describes the structure of the Single Cycle Machine which is shown in the attached picture. Use the following names for the modules so everyone's code will be compatible. Module Name Purpose Number of Instances regfile Register File Program Counter pc counter inst anna Instruction RAM 1 data ram Data RAM control Computer Controller 1 mux 2 1 by 5 2 to 1 Mux 5 data bits Lalu Arithmetic Logic Unit 1 4 mux 2 1 by 32 2 to 1 Mux 32 data bits shifter left shifter or multiply by 4 2 sign extender Sign extend 2 adder Instruction Counter Notice that this is not the machine of the textbook. We are going to let the synthesizer determine the ALUcontrol. Be careful, not all of the widths of the vectors are given in the diagram. What size should the vectors be? The machine is to be BIG Endian just like MIPS. You may either use NoMachine or a working version of Xilinx on your laptop. Note that there many ways to handle the shifter circuitry including not having a shifter at all and using the Concatenation operator in Verilog. For example, the input to the mux could be poded using the following assignment: assign wire [31:0l mux addr- PC 4131:28], Intruction[25:0], 2'b0), Feel free to use this technique. Write the Verilog which describes the structure of the Single Cycle Machine which is shown in the attached picture. Use the following names for the modules so everyone's code will be compatible. Module Name Purpose Number of Instances regfile Register File Program Counter pc counter inst anna Instruction RAM 1 data ram Data RAM control Computer Controller 1 mux 2 1 by 5 2 to 1 Mux 5 data bits Lalu Arithmetic Logic Unit 1 4 mux 2 1 by 32 2 to 1 Mux 32 data bits shifter left shifter or multiply by 4 2 sign extender Sign extend 2 adder Instruction Counter Notice that this is not the machine of the textbook. We are going to let the synthesizer determine the ALUcontrol. Be careful, not all of the widths of the vectors are given in the diagram. What size should the vectors be? The machine is to be BIG Endian just like MIPS. You may either use NoMachine or a working version of Xilinx on your laptop. Note that there many ways to handle the shifter circuitry including not having a shifter at all and using the Concatenation operator in Verilog. For example, the input to the mux could be poded using the following assignment: assign wire [31:0l mux addr- PC 4131:28], Intruction[25:0], 2'b0), Feel free to use this technique