Answered step by step

Verified Expert Solution

Question

1 Approved Answer

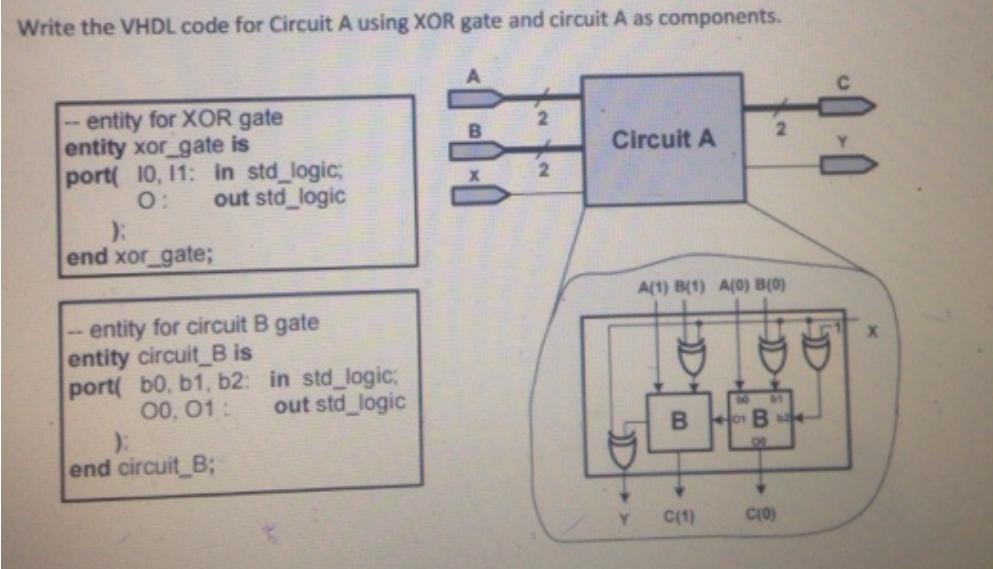

Write the VHDL code for Circuit A using XOR gate and circuit A as components. entity for XOR gate entity xor_gate is port( 10,

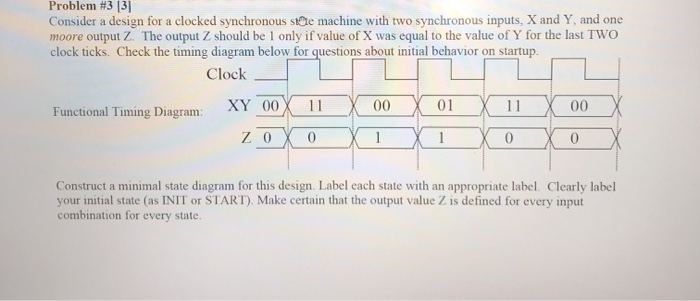

Write the VHDL code for Circuit A using XOR gate and circuit A as components. entity for XOR gate entity xor_gate is port( 10, 11: in std_logic; O: out std_logic ); end xor_gate; entity for circuit B gate entity circuit B is port( b0, b1, b2: in std_logic; 00, 01: out std_logic end circuit B; 2 Circuit A D Y A(1) B(1) A(0) B(0) B C(1) 2 01 B C(0) Problem #3 [3] Consider a design for a clocked synchronous state machine with two synchronous inputs, X and Y, and one moore output Z. The output Z should be 1 only if value of X was equal to the value of Y for the last TWO clock ticks. Check the timing diagram below for questions about initial behavior on startup. Clock Functional Timing Diagram: XY 00 11 ZOO 00 1 01 1 11 0 00 0 X Construct a minimal state diagram for this design. Label each state with an appropriate label. Clearly label your initial state (as INIT or START). Make certain that the output value Z is defined for every input combination for every state.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started