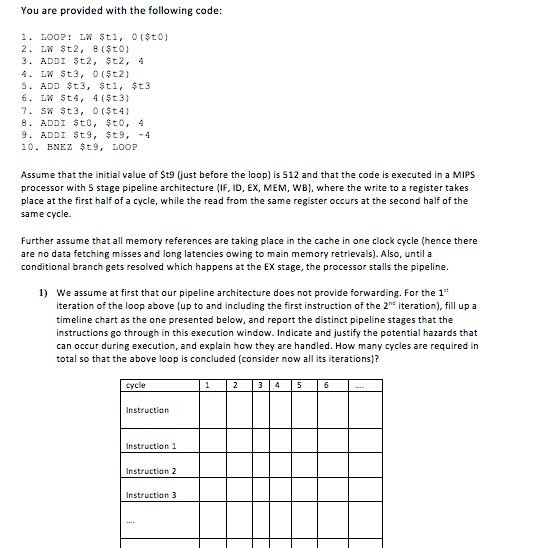

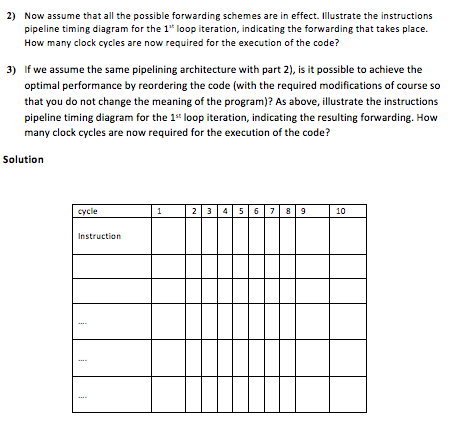

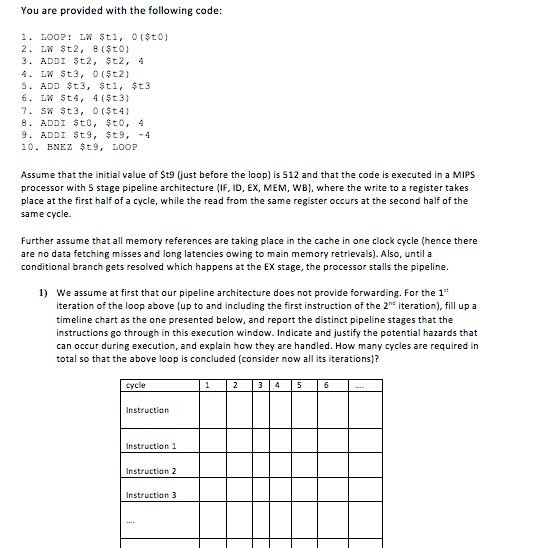

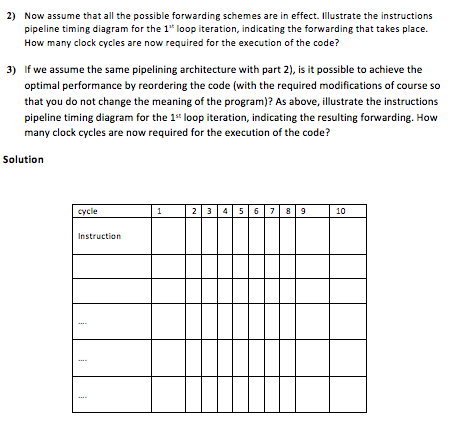

You are provided with the following code: . ADDI $t2, $t2, 4 4. LW $t3, 0 ($t2) 5.ADD $t3, Sti, $t3 ADDI StO, $to, ADDI St9, $t9, -4 10. BNEZ $t9, LOOP Assume that the initial value of $t9(just before the loop] is 512 and that the code is executed in a MIPS processor with 5 stage pipeline architecture (IF, ID, EX, MEM, WB), where the write to a register takes place at the first half of a cycle, while the read from the same register occurs at the second half of the same cycle. Further assume that all memory references are taking place in the cache in one clock cycle (hence there are no data fetching misses and long latencies owing to main memory retrievals). Also, until a conditional branch gets resolved which happens at the EX stage, the processor stalls the pipeline. 1) We assume at first that our pipeline architecture does not provide forwarding. For the 1 iteration of the loop above (up to and including the first instruction of the 2n iteration), fill up a timeline chart as the one presented below, and report the distinct pipeline stages that the instructions go through in this execution window. Indicate and justify the potential hazards that can occur during execution, and explain how they are handled. How many cycles are required in total so that the above loop is concluded (consider now al its iterations)? Instruction Instruction 1 Instruction 2 Instruction 3 You are provided with the following code: . ADDI $t2, $t2, 4 4. LW $t3, 0 ($t2) 5.ADD $t3, Sti, $t3 ADDI StO, $to, ADDI St9, $t9, -4 10. BNEZ $t9, LOOP Assume that the initial value of $t9(just before the loop] is 512 and that the code is executed in a MIPS processor with 5 stage pipeline architecture (IF, ID, EX, MEM, WB), where the write to a register takes place at the first half of a cycle, while the read from the same register occurs at the second half of the same cycle. Further assume that all memory references are taking place in the cache in one clock cycle (hence there are no data fetching misses and long latencies owing to main memory retrievals). Also, until a conditional branch gets resolved which happens at the EX stage, the processor stalls the pipeline. 1) We assume at first that our pipeline architecture does not provide forwarding. For the 1 iteration of the loop above (up to and including the first instruction of the 2n iteration), fill up a timeline chart as the one presented below, and report the distinct pipeline stages that the instructions go through in this execution window. Indicate and justify the potential hazards that can occur during execution, and explain how they are handled. How many cycles are required in total so that the above loop is concluded (consider now al its iterations)? Instruction Instruction 1 Instruction 2 Instruction 3