Answered step by step

Verified Expert Solution

Question

1 Approved Answer

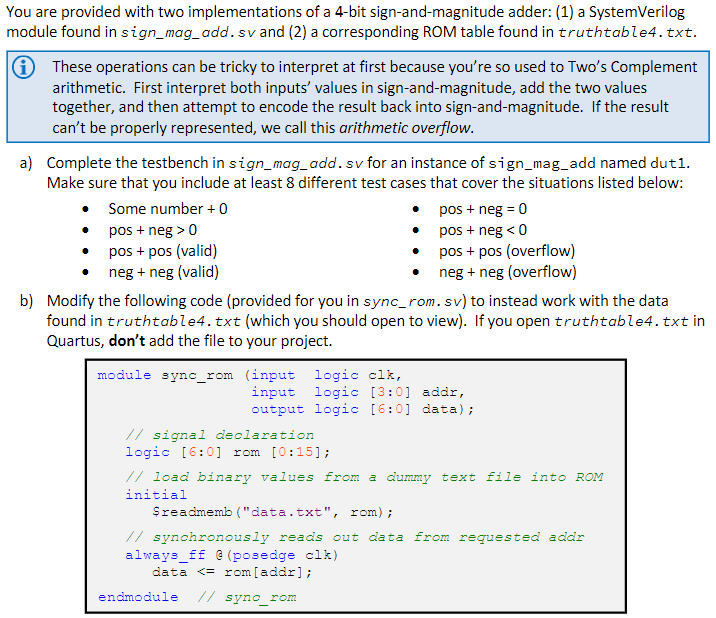

You are provided with two implementations of a 4-bit sign-and-magnitude adder: (1) a SystemVerilog module found in sign_mag_add.svand (2) a corresponding ROM table found

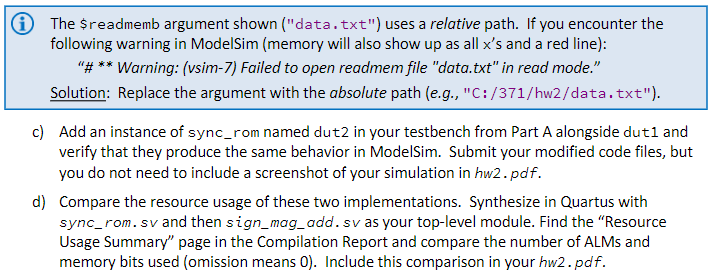

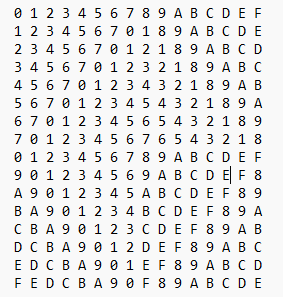

You are provided with two implementations of a 4-bit sign-and-magnitude adder: (1) a SystemVerilog module found in sign_mag_add.svand (2) a corresponding ROM table found in truthtable4.txt. These operations can be tricky to interpret at first because you're so used to Two's Complement arithmetic. First interpret both inputs' values in sign-and-magnitude, add the two values together, and then attempt to encode the result back into sign-and-magnitude. If the result can't be properly represented, we call this arithmetic overflow. a) Complete the testbench in sign_mag_add. sv for an instance of sign_mag_add named dut1. Make sure that you include at least 8 different test cases that cover the situations listed below: Some number + 0 pos + neg > 0 pos + pos (valid) neg + neg (valid) b) Modify the following code (provided for you in sync_rom.sv) to instead work with the data found in truthtable4.txt (which you should open to view). If you open truthtable4.txt in Quartus, don't add the file to your project. module sync_rom (input input pos + neg = 0 pos + neg < 0 pos + pos (overflow) neg + neg (overflow) logic clk, logic [3:0] addr, output logic [6:0] data); // signal declaration logic [6:0] rom [0:15]; // load binary values from a dummy text file into ROM initial $readmemb ("data.txt", rom); // synchronously reads out data from requested addr always_ff @ (posedge clk) data The $readmemb argument shown ("data.txt") uses a relative path. If you encounter the following warning in ModelSim (memory will also show up as all x's and a red line): "#** Warning: (vsim-7) Failed to open readmem file "data.txt" in read mode." Solution: Replace the argument with the absolute path (e.g., "C:/371/hw2/data.txt"). c) Add an instance of sync_rom named dut2 in your testbench from Part A alongside dut1 and verify that they produce the same behavior in ModelSim. Submit your modified code files, but you do not need to include a screenshot of your simulation in hw2.pdf. d) Compare the resource usage of these two implementations. Synthesize in Quartus with sync_rom.sv and then sign_mag_add. sv as your top-level module. Find the "Resource Usage Summary" page in the Compilation Report and compare the number of ALMs and memory bits used (omission means 0). Include this comparison in your hw2.pdf. 0 1 2 3 4 5 6 7 8 9 A B C D E F 1 2 3 4 5 6 7 0 1 8 9 A B C D E 2 3 4 5 6 7 0 1 2 1 8 9 A B C D 3 4 5 6 7 0 1 2 3 2 1 89 A B C 4 5 6 7 0 1 2 3 4 3 2 18 9 A B 5 6 70 1 2 3 4 5 4 3 2 1 8 9 A 6 70 1 2 3 4 5 6 5 4 3 2 189 70 1 2 3 4 5 6 7 6 5 4 3 2 1 8 0 1 2 3 4 5 6 7 8 9 A B C D E F 9 0 1 2 3 4 5 6 9 A B C D E F 8 A 9 0 1 2 3 4 5 A B C D E F 89 BA 9 0 1 2 3 4 B C D E F 89 A C B A 9 0 1 2 3 C D E F 8 9 A B D C B A 9 0 1 2 D E F 8 9 A BC EDC BA 9 0 1 E F 8 9 A B C D FED CBA 9 0 F 8 9 A B C D E

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started